#### Abstract

AZIDEHAK, ALI. Design of Fault-tolerant Controller for Modular Multi-level Converters. (Under the direction of Dr. Subhashish Bhattacharya.)

Almost all power electronic circuits are using a digital controller to drive switching devices, handle faults, measure signals and communicate to other systems. The controller for most applications is required to have high degree of robustness, since the failure can cost money or may cause serious injuries to people. Therefore it is necessary to find out if the controller is functioning correctly and if it is not, required procedures must be done to handle the failure. The first fault-tolerant computer was designed in 1950 and its application was limited to stationary systems such as nuclear plant control system. By 1970, microprocessor developments made it easy to embed chips into every device. There was a big problem with such microprocessors when used in critical applications like aerospace. A failure in the controller could fail the whole project; therefore it needed some layers of protection against faults. Lots of efforts have been done to design a fault-tolerant controller which is the base for this research and will be discussed in the following chapters.

Application of fault-tolerant controllers is not limited to high-end products and even in commercial products like servers, fault-tolerant and non-stop machine is required for packet processing, data storage and computation. With advancement in power electronic systems and control theories, microprocessors become popular in designs. There are more difficulties in power electronic circuits than other systems. The operating frequency of power circuits can exceed hundreds of kilo hertz; therefore real-time response to failure is one of the challenges in the design. Any fault in the controller should be diagnosed instantly; otherwise it is possible to get destructive overshoots in voltage or current. There are also different converter topologies and some need specific controller architecture. It is not possible to use one controller in every design. One of the new topologies is Modular Multi-level Converter (MMC) that is going under lots of test and development. The biggest benefit associated with this topology is modularity and ability to work even when a fault has happened in one of the modules [8]. To get the most of this converter, controllers should also be fault proof and if a fault happens to one of the controllers, it should be diagnosed and other controller should take the responsibility. That means having no single point of failure in the system and single fault can never interrupt the functionality of the system. The goal of this report is to review researches that have been done for designing fault-tolerant systems and use it for power electronic controllers. In the first chapter, an introduction to the research will be presented. It will define the motivation for this research and the contribution of this dissertation. In second chapter, the techniques for designing a distributed controller system will be investigated. The techniques presented will be about control and synchronization of distributed controllers using a supervisory controller. Third chapter would focus on the architecture of the fault-tolerant controller and failure in the controller systems. Fourth chapter focus on reliability assessment which is a process in fault-tolerant controllers to reveal the perfectness of the functionality and Markov chain is the mathematical tool to model each controller's reliability. Fifth chapter is about firmware design and techniques to avoid failure in the system as much as it is possible. Sixth chapter presents experimental result for two types of converter including modular multi-level converter (MMC) and cascaded h-bridge converter (CHB). Seventh chapter makes the final conclusion and proposes the future researches in this field.

© Copyright 2017 by Ali Azidehak

All Rights Reserved

#### Design of Fault-tolerant Controller for Modular Multi-level Converters

by Ali Azidehak

#### A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

Electrical Engineering

Raleigh, North Carolina

2017

APPROVED BY:

Dr. Alexander Dean

Dr. Srdjan Lukic

Dr. Xiangwu Zhang

Dr. Subhashish Bhattacharya Chair of Advisory Committee

## Dedication

To whom, we are waiting for his appearance.

تقدیم به آنکه انتظار ظهورش را می کشیم.

\*\*\*\*\*

To my parents, Fakhri Shahin & Asghar Azidehak.

تقديم به پدر و مادر عزيزم.

\*\*\*\*\*

To my siblings, Farnaz, Amir & Faranak.

تقدیم به خواهران و برادر عزیزم، فرناز، امیر و فرانک.

#### **Biography**

Ali Azidehak was born in Esfahan, Iran. During his life, experiencing new things and researching about new subjects, was one of the priorities in the life for him. It started with a junior robotic team which participated in international competitions. He continued his dream and received his B.Sc in Electrical Engineering from Islamic Azad University at Qazvin, Iran. During B.Sc, He has worked in the Mechatronics Research Lab for 4 years and has participated in several Robocup international competitions. In 2012, he started M.Sc in Electrical Engineering at North Carolina State University in Raleigh, NC. He started his research under supervision of Dr.Bhattacharya at Future Renewable Electric Energy Delivery and Management(FREEDM) systems center. During this period, he has worked on broad area of power electronics systems, as well as embedded controller circuits. After completing the M.Sc, He continued PhD under the same advisor and co-advising of Dr.Alexander Dean with focus on the fault-tolerant controller architectures that can be used in power electronics. He has also worked as intern for period of six months in Robert Bosch research center in Charlotte, NC and did research on DC micro-grid systems. The dissertation presented here is based on his research in FREEDM research center about fault-tolerant controller architectures with focus on power electronics application.

#### Acknowledgements

I would like to thank my parents for their moral and financial support. They made it possible for me to get my degree from NCSU.

\*\*\*

I would like to thank Dr. Subhashish Bhattacharya for funding and supporting me academically.

\*\*\*

I would like to thank Dr. Alexander Dean for co-advising and Dr. Srdjan Lukic and Dr. Xianwu Zhang as committee members.

\*\*\*

FREEDM research center and its employees made it possible for students to reach their goals. Thank you for your help.

\*\*\*

Special thanks to employees of Robert Bosch LLC in Charlotte, NC whom we've had great time and learned a lot together.

\*\*\*

I'd like to thank my friends who helped me during my education. Specially Mark Hwang, Rajat Agarwal and Prasanth Gomatam who helped me preparing the experimental setup.

## **Table of Contents**

| List of Tables       |                                                                               |     |

|----------------------|-------------------------------------------------------------------------------|-----|

| List of I            | Figures                                                                       | iii |

| Chapte               | r 1 Introduction                                                              | 1   |

| 1.1                  | Research Background                                                           | 1   |

|                      | 1.1.1 Tandem Computer                                                         | 2   |

|                      | 1.1.2 NASA Shuttle Guidance System                                            | 3   |

|                      | 1.1.3 Automotive Control Units                                                | 4   |

|                      | 1.1.4 Fault-tolerant WSI/VLSI Architecture                                    | 6   |

| 1.2                  | Motivation                                                                    | 9   |

|                      | 1.2.1 Comparison of Multi-level Converters and Feasibility of Using Dis-      |     |

|                      | tributed Fault-tolerant Controller                                            | 9   |

|                      | 1.2.2 Performance and Reliability Enhancement in Power Delivery using         |     |

|                      | Modular Multi-level Converter with Distributed Fault-tolerant Controller      | 11  |

| 1.3                  | Research Contributions                                                        | 14  |

|                      |                                                                               |     |

| Chapte               |                                                                               |     |

| 0.1                  |                                                                               | 16  |

| 2.1                  |                                                                               | 16  |

| 2.2                  |                                                                               | 17  |

| 2.3                  |                                                                               | 22  |

| 2.4                  | Implementation of Clock Synchronization in First Generation of Fault-tolerant | ~ ~ |

| 0.5                  | 6                                                                             | 25  |

| 2.5                  | Second Generation of Fault-tolerant Controller and Dominant Output (DOMINO)   | 0.1 |

|                      | 5 6                                                                           | 31  |

|                      | 5                                                                             | 31  |

|                      |                                                                               | 34  |

|                      |                                                                               | 37  |

| 2.6                  |                                                                               | 39  |

| 2.6                  | Timing Consideration in Design of Distributed Controllers                     | 41  |

| Chapte               | r 3 Fault-tolerant Controller Architecture for Modular Multi-level Con-       |     |

| - · · <b>I</b> · · · |                                                                               | 44  |

| 3.1                  |                                                                               | 44  |

| 3.2                  |                                                                               | 45  |

|                      | •                                                                             | 45  |

| 3.3                  |                                                                               | 49  |

|                      |                                                                               | 49  |

|         | 3.3.2 Evolution of Fault-tolerant Distributed Controlled Power Modules            | 54  |

|---------|-----------------------------------------------------------------------------------|-----|

|         | 3.3.3 Second Generation of Fault-tolerant Distributed Controller                  | 60  |

| 3.4     | Proposed Distributed Fault-tolerant Controller for Modular Multi-level Converters | 62  |

|         | 3.4.1 Architecture of Fault-tolerant Controller for MMC                           | 62  |

|         | 3.4.2 Fault Detection in Converter Modules                                        | 64  |

|         | 3.4.3 Fail-over Strategy                                                          | 67  |

| 3.5     | 1                                                                                 | 69  |

|         |                                                                                   | 70  |

|         |                                                                                   | 71  |

|         | e                                                                                 | 72  |

| 3.6     | 1                                                                                 | 77  |

|         | 1 1                                                                               | 83  |

|         | <b>▲</b>                                                                          | 86  |

|         |                                                                                   | 89  |

|         | 3.6.4 Converter Output Result at Controller Synchronization Failure(Mode 3)       | 91  |

| Chapter | r 4 Reliability Assessment of Proposed Fault-tolerant Controller Architec-        |     |

| Chapter | · ·                                                                               | 93  |

| 4.1     |                                                                                   | 93  |

| 4.2     |                                                                                   | 94  |

|         | 5                                                                                 | 94  |

|         |                                                                                   | 97  |

| 4.3     | Reliability Prediction for Controller Components                                  |     |

|         | 4.3.1 Failure Rate Calculation for Controller Card                                |     |

| 4.4     | Monte Carlo Simulation for Reliability Estimation of the Proposed Controller . 1  |     |

| 4.5     | Markov Process and Reliability Assessment                                         |     |

|         | 4.5.1 Markov Model of Common Fault-tolerant Controllers                           |     |

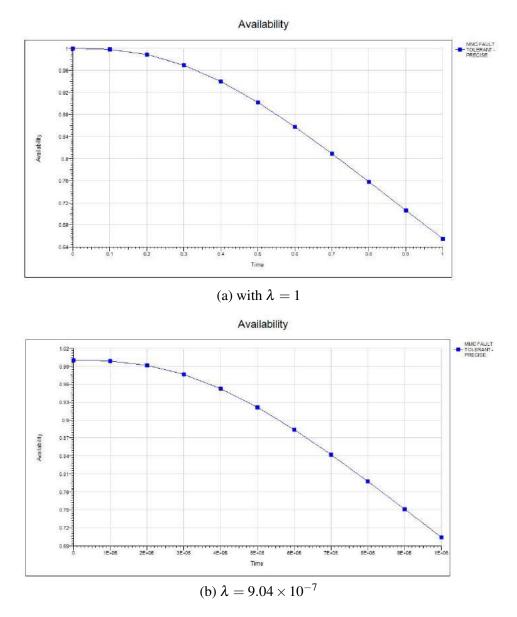

| 4.6     | Computer Aided Reliability Assessment of the Markov Chain Model 1                 | 21  |

|         |                                                                                   | • • |

| Chapte  | 8 I                                                                               |     |

| 5.1     | Introduction                                                                      |     |

| 5.2     | Software Fault Categorization                                                     |     |

| 5.3     | Fault Avoidance Techniques in Firmware Design                                     | 31  |

|         | 5.3.1 MISRA-C Coding Style and Application in Fault-tolerant Firmware             | 21  |

|         | Design                                                                            |     |

|         | 5.3.2 Software Partitioning                                                       |     |

|         | 5.3.3 Scheduling, Timing and Interactions                                         |     |

| 5 1     | 5.3.4 Software Rejuvenation                                                       |     |

| 5.4     | Fault-tolerant Firmware Design Methods    1      5.4.1    Numerical Programming   |     |

|         | 5.4.1 N-version Programming                                                       |     |

|         | 5.4.2 Recovery Blocks                                                             | 4/  |

|         |                                                                                   |     |

| 5.5     | Consensus on Selection of the Master Controller in Second Generation of Fault-  |     |

|---------|---------------------------------------------------------------------------------|-----|

|         | tolerant Controller                                                             | 48  |

| Chapte  | r 6 Implementation and Experimental Verification of Proposed Fault-tolerant     | t   |

|         | Controller for Modular Multi-level Converters                                   | 54  |

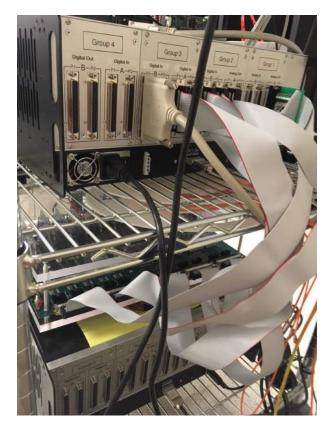

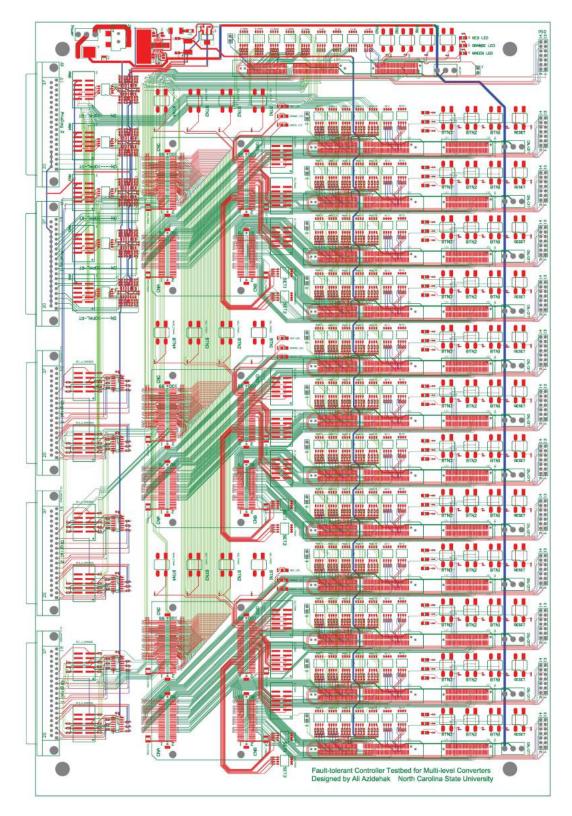

| 6.1     | Implementation of Proposed Methods on the Fault-tolerant Controller Test-bed 1  | 55  |

| 6.2     | Theory of Operation for Hardware in the Loop (HIL) Simulation                   | 58  |

| 6.3     | Hardware in the Loop Simulation for the Proposed Fault-tolerant Controller 1    | 61  |

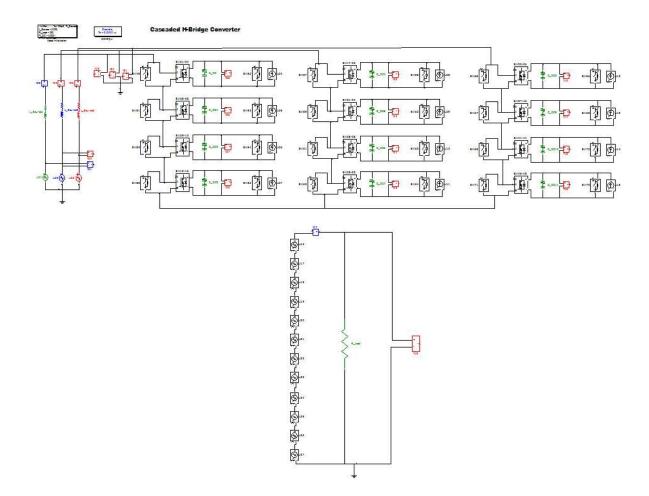

| 6.4     | Hardware in the Loop Simulation Result for Cascaded H-bridge Converter Using    |     |

|         | Fault-tolerant Controller                                                       | 63  |

|         | 6.4.1 Cascaded H-bridge Converter under Normal Operation                        | 65  |

|         | 6.4.2 Fault Injection Result In Controller Architecture for Cascaded H-bridge   |     |

|         | Converter                                                                       | 68  |

| 6.5     | Hardware in the Loop Simulation Result for Modular Mult-level Converter         |     |

|         | Using Fault-tolerant Controller                                                 | 86  |

|         | 6.5.1 Modular Multi-level Converter under Normal Operation                      | 88  |

|         | 6.5.2 Fault Injection Result In Controller Architecture for Modular Multi-level |     |

|         | Converter                                                                       | 91  |

| 6.6     | Real Hardware Experimental Result for Cascaded H-bridge Converter Using         |     |

|         | Fault-tolerant Converter    2                                                   | .06 |

| Chapte  | r 7 Conclusion and Future Works                                                 | 21  |

| 7.1     | Conclusions                                                                     | 21  |

| 7.2     | Proposed Future Works                                                           | .23 |

| Referen | nces                                                                            | 24  |

| Append  | lices                                                                           | 32  |

|         | endix A Distributed Control Stages for Cascaded H-bridge Multi-level Converter2 |     |

| Арр     | endix B Distributed Control Stages for Modular Multi-level Converter 2          | 241 |

| App     | endix C Schematics and Design of Fault-tolerant Controller Testbed 2            |     |

# List of Tables

| Table 2.1 | Comparison between Architectures of Different Distributed Controller Systems 21   |

|-----------|-----------------------------------------------------------------------------------|

| Table 3.1 | Comparison Between Static and Dynamic Redundant Controllers[92] 48                |

| Table 3.2 | Power Parameters for Simulated Fault-tolerant Controller of Cascaded H-bridge 82  |

| Table 4.1 | Prediction Methods for Electronic Components Failure                              |

| Table 4.2 | Mean Failure Rate of Critical Components in TI-F28377 Control Card 103            |

| Table 4.3 | Markov Model Types                                                                |

| Table 4.4 | Summary of Reliability Analysis for Proposed Controller and Other Controllers 128 |

| Table 5.1 | Software Safety Level and Its Impact Factor                                       |

| Table 5.2 | Execution Time for Main Tasks in Master Controller                                |

| Table 5.3 | Execution Time for Main Tasks in Slave Controller                                 |

| Table 5.4 | Classes of Aging Related Bugs in Software                                         |

| Table 6.1 | Setup Configuration for CHB HIL Simulation                                        |

| Table 6.2 | Setup Configuration for MMC HIL Simulation                                        |

| Table 6.3 | Setup Configuration for CHB Hardware Experimental Setup                           |

|           |                                                                                   |

# List of Figures

| Figure 1.1  | Original Architecture of Tandem Computer (1976)                                    | 3     |

|-------------|------------------------------------------------------------------------------------|-------|

| Figure 1.2  | Block Diagram of NASA Shuttle Data Processing System                               | 4     |

| Figure 1.3  | Architecture of Tricore <sup>TM</sup> ver-1.6 Automotive Micro-controller[2]       | 5     |

| Figure 1.4  | Re-configurable Processor Array (a)Before Configuration (b)After Configu-          |       |

| C           | ration                                                                             | 6     |

| Figure 1.5  | Architecture of Array Processor with Spare Processing Element at the Edges         | 7     |

| Figure 1.6  | Diagram of Two Non-modular Multi-level Converters                                  | 10    |

| Figure 1.7  | Renewable Energy Usage by Each Country                                             | 11    |

| Figure 1.8  | Diagram of Modular Multi-level Converters [54]                                     | 12    |

| Figure 2.1  | Daisy-Chain Distributed Controller Architecture                                    | 18    |

| Figure 2.2  | Parallel Distributed Controller Architecture                                       | 19    |

| Figure 2.3  | Parallel-Daisy Distributed Controller Architecture                                 | 20    |

| Figure 2.4  | Example of Data Flow Diagram (Capacitor Voltage) between Master and                |       |

|             | Slave Controllers                                                                  | 27    |

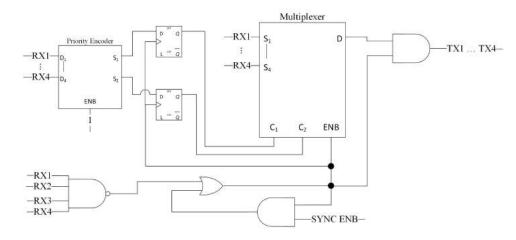

| Figure 2.5  | PWM Phase Synchronization Hardware for Slave Controllers                           | 28    |

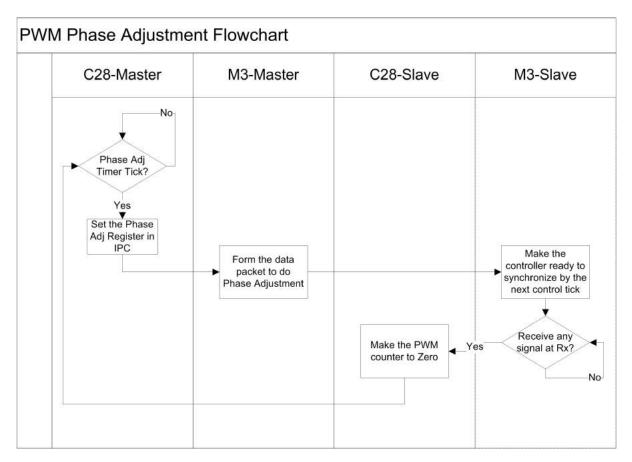

| Figure 2.6  | PWM Phase Synchronization Flowchart                                                | 29    |

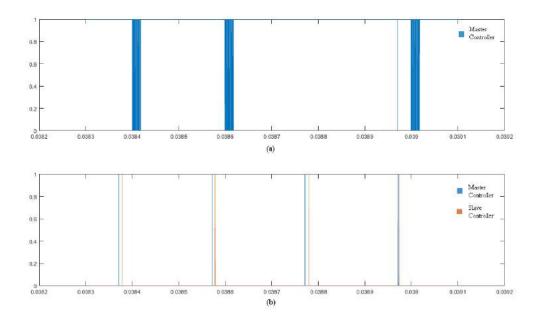

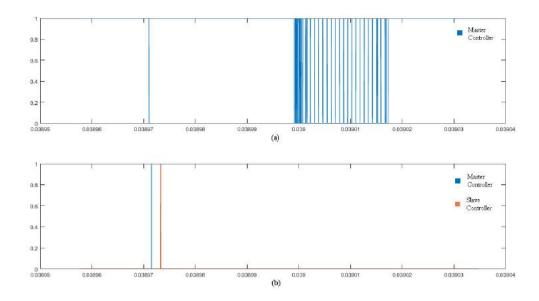

| Figure 2.7  | Synchronization Procedure in Proposed Controller (a)Data Packet Sent by            |       |

|             | the Master Controller (b)Phase Zero-crossing for Slave and Master Controllers      | 30    |

| Figure 2.8  | Magnified Synchronization Procedure after Initialization of Process by             |       |

|             | Master Controller                                                                  | 30    |

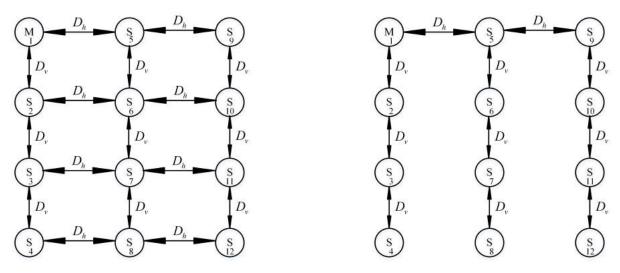

| Figure 2.9  | Graph Representation of the Second Generation Controller                           | 32    |

| Figure 2.10 | Hardware Implementation of DOMINO Synchronization Algorithm                        | 36    |

| Figure 2.11 | Simulation Result for DOMINO Algorithm                                             | 36    |

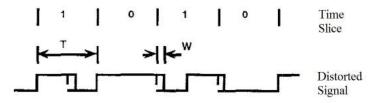

| Figure 2.12 | Pulse Width Distortion in Fiber Optic Output Signal at Receiver                    | 39    |

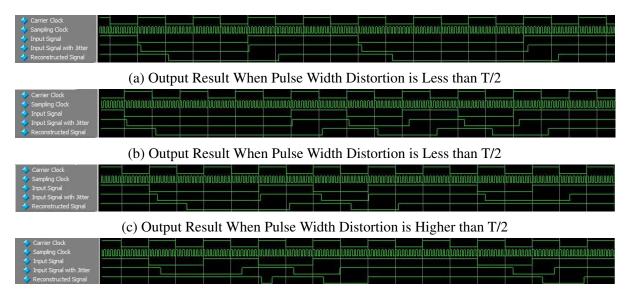

| Figure 2.13 | Result of the Correcting Circuit at each Repeater Module                           | 40    |

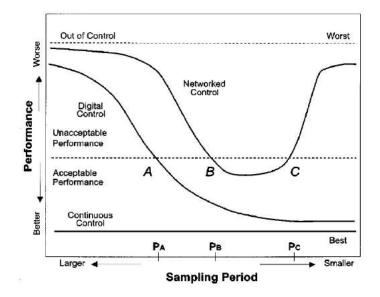

| Figure 2.14 | Performance of Control Systems versus Sampling Time                                | 41    |

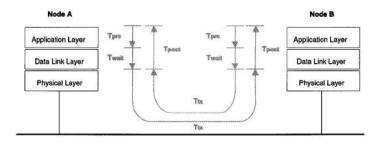

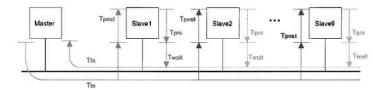

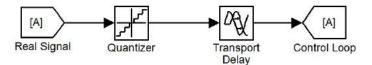

| Figure 2.15 | Time Diagram Showing the Time Spend to Transfer Data Between Different             |       |

| -           | Node of a Network Control System                                                   | 42    |

| Figure 2.16 | Waiting Time Diagram                                                               | 42    |

| Figure 2.17 |                                                                                    | 43    |

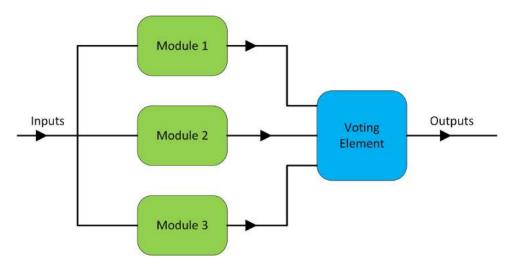

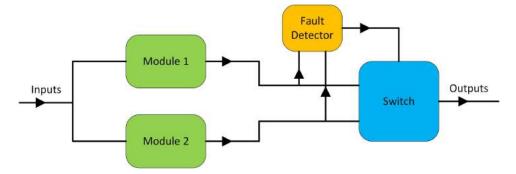

| Figure 3.1  | Architecture of Triple Modular Redundancy                                          | 46    |

| Figure 3.2  | Architecture of Standby Redundant System                                           | 48    |

| Figure 3.3  | Architecture of Array Processors Proposed by Kailath                               | 50    |

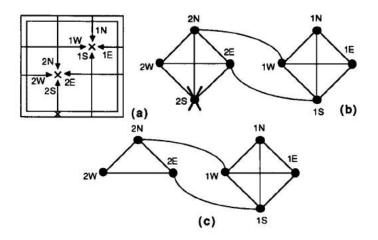

| Figure 3.4  | (a)-(f)Screening process, (g)Equivalent fault pattern after screening, (h)Contradi | ction |

|             | graph for (g), (i)The placement solution                                           | 51    |

| Figure 3.5  | (a)Fault pattern, (b)Corresponding contradiction graph with a "crossed"                |    |

|-------------|----------------------------------------------------------------------------------------|----|

|             | vertex, (c)Reduced equivalent contradiction graph                                      | 52 |

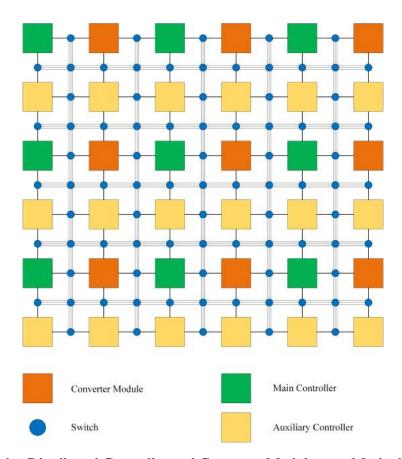

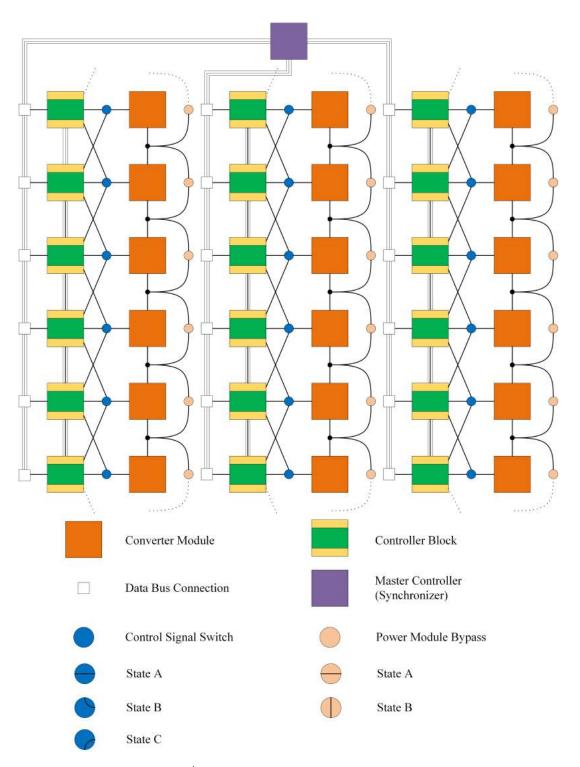

| Figure 3.6  | Distributed Controller and Converter Module over Meshed Network                        | 54 |

| Figure 3.7  | Omission of Unusable Auxiliary Controllers from the Grid                               | 55 |

| Figure 3.8  | Embedding the Auxiliary Controllers Inside the Main Controllers                        | 56 |

| Figure 3.9  | Omission of Unused Space and Integrating the Power Modules and Controllers             | 56 |

| Figure 3.10 | Architecture of Customized Array Interconnections for Power Electronics                |    |

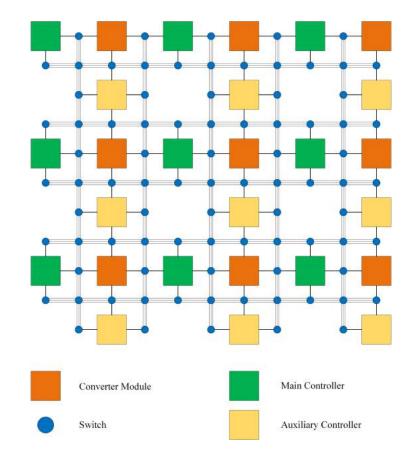

| C           | Application                                                                            | 57 |

| Figure 3.11 | Architecture of 1 <sup>st</sup> Generation Fault-tolerant Distributed Controlled Power |    |

| C           | Modules                                                                                | 59 |

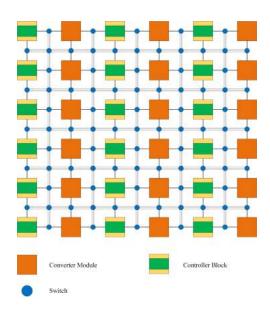

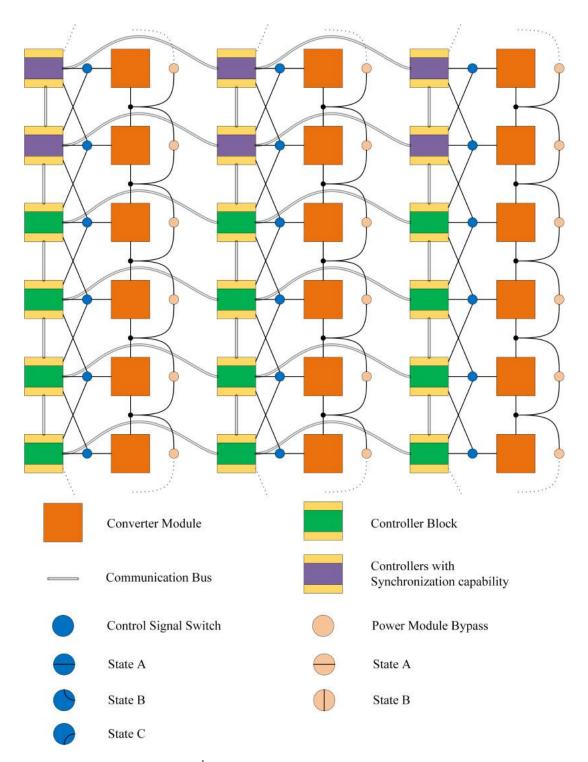

| Figure 3.12 | Architecture of 2 <sup>nd</sup> Generation Fault-tolerant Distributed Controlled Power |    |

| C           | Modules                                                                                | 61 |

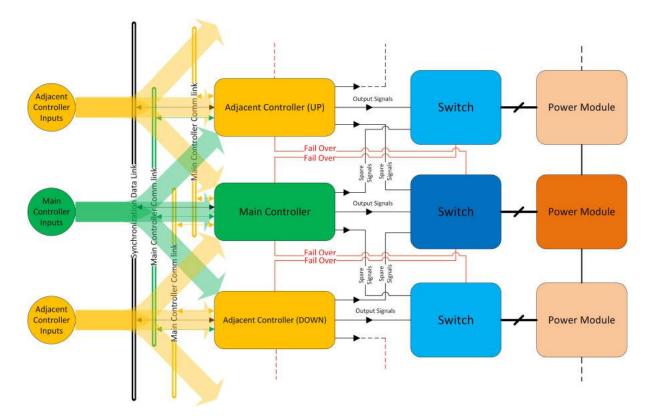

| Figure 3.13 |                                                                                        | 63 |

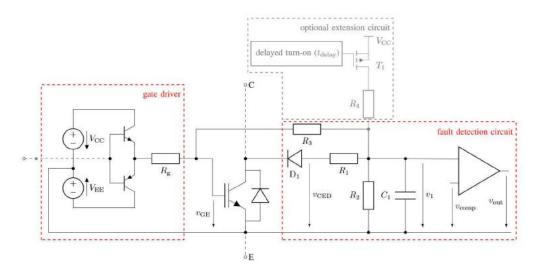

| Figure 3.14 | IGBT Fault Detection Based on Desaturation Checking                                    | 64 |

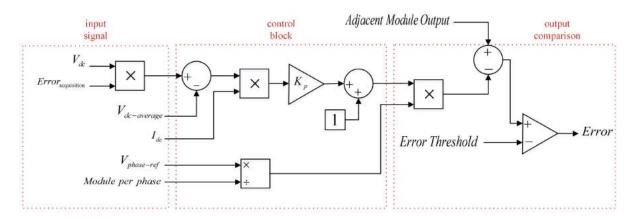

| Figure 3.15 | -                                                                                      | 65 |

| Figure 3.16 | Watchdog Timer for Detection of Communication and Controller Failure                   | 66 |

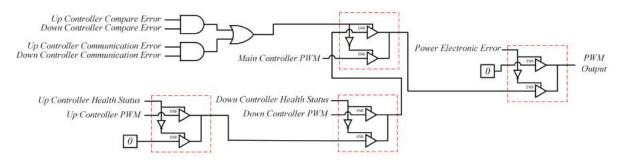

| Figure 3.17 | Fail-over Strategy Diagram in each Module                                              | 67 |

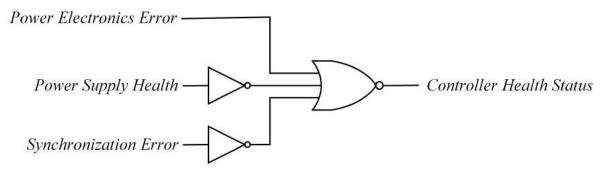

| Figure 3.18 | Diagram of Controller Health Indicator                                                 | 68 |

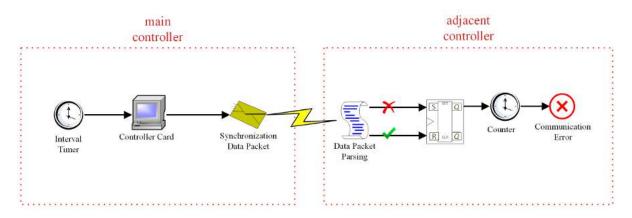

| U           | Controller Architecture During Synchronization Mechanism                               | 72 |

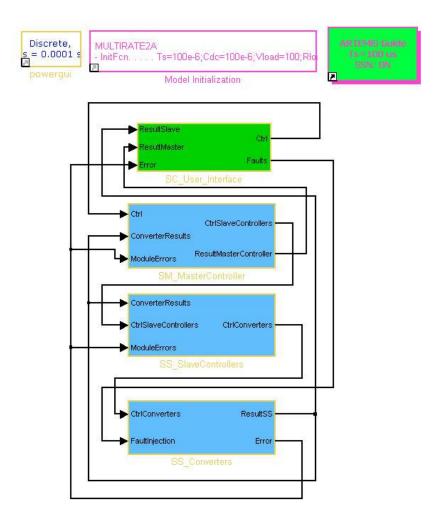

| Figure 3.20 | •••                                                                                    | 77 |

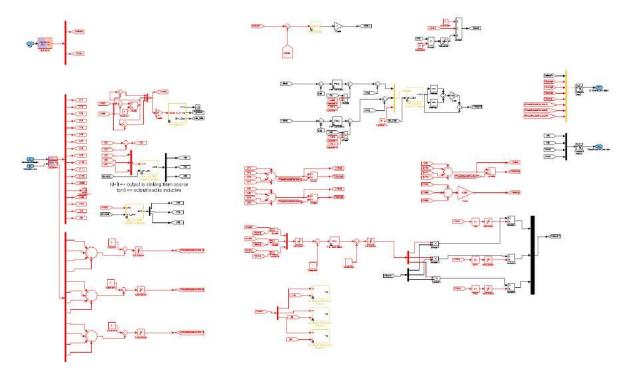

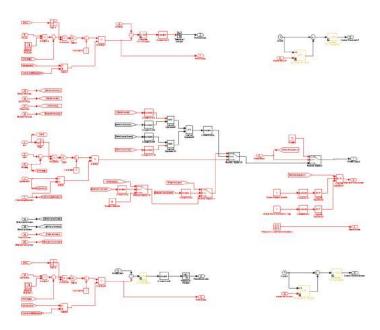

| Figure 3.21 | Simulation Diagram of Master Controller                                                | 78 |

| Figure 3.22 | Simulation Diagram of Slave Controllers                                                | 79 |

| Figure 3.23 | Connection between Slave Controllers                                                   | 79 |

| Figure 3.24 | Slave Controllers at the Edge of the Converter Leg                                     | 80 |

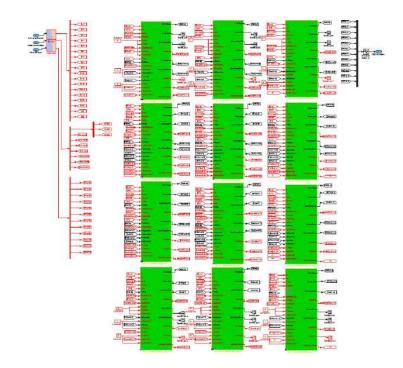

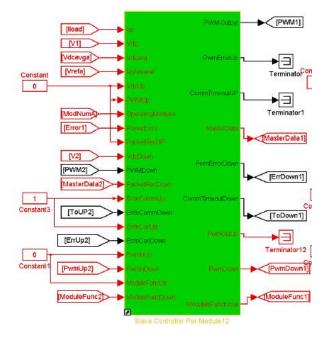

| Figure 3.25 | Internal Block Diagram of Slave Controllers                                            | 80 |

| Figure 3.26 | Block Diagram of Multi-level Converter                                                 | 81 |

| Figure 3.27 | Internal Block Diagram of Converter Modules                                            | 82 |

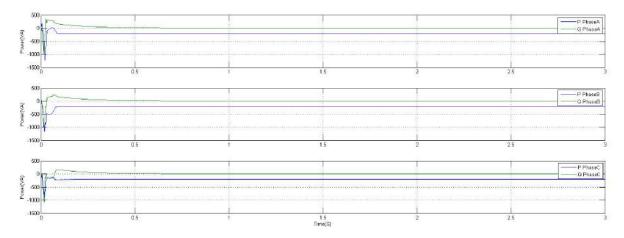

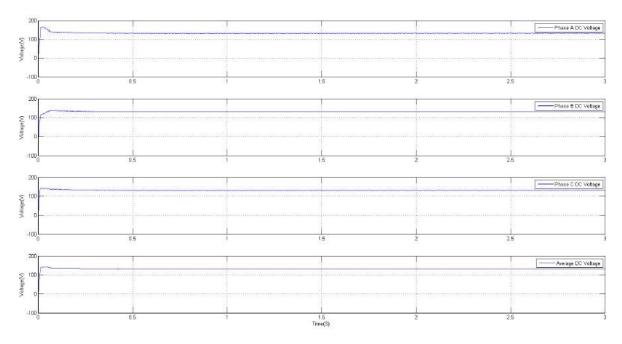

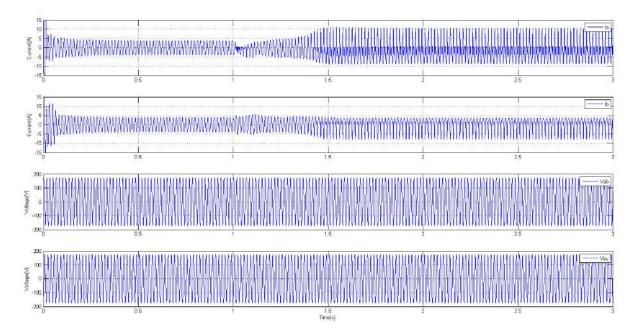

| Figure 3.28 | Grid Voltage and Current at Normal Operation of Converter                              | 83 |

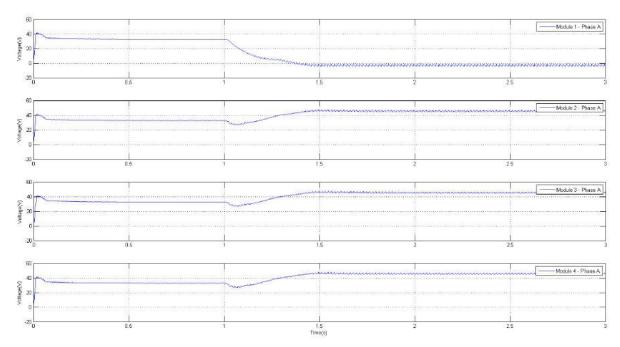

| Figure 3.29 |                                                                                        | 84 |

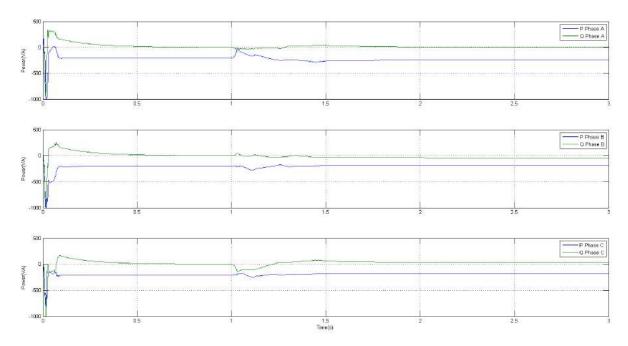

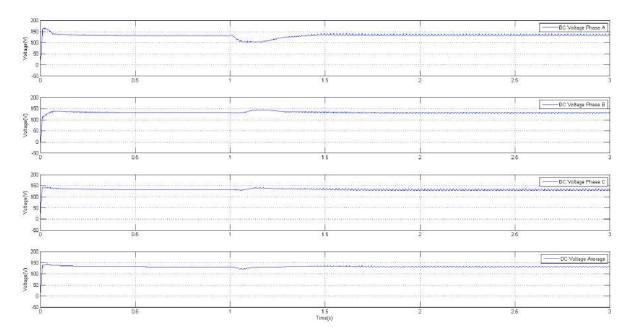

| Figure 3.30 | DC Voltage of each Phase at Normal Operation of Converter                              | 84 |

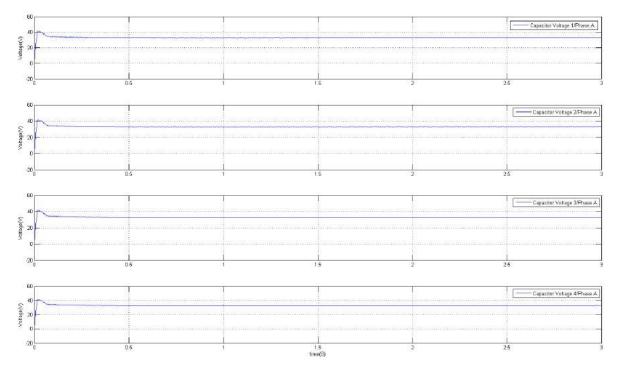

| Figure 3.31 | Module Capacitor Voltages for Phase A at Normal Operation of Converter .               | 85 |

| Figure 3.32 | Grid Voltage and Current when Failure Happens in Power Module at t=1s .                | 86 |

| Figure 3.33 | Grid Phase Power when Failure Happens in Power Module at t=1s                          | 87 |

| Figure 3.34 | DC Voltage of each Phase when Failure Happens in Power Module at t=1s.                 | 88 |

| Figure 3.35 | Module Capacitor Voltages for Phase A when Failure Happens in Power                    |    |

| c           | Module at t=1s                                                                         | 88 |

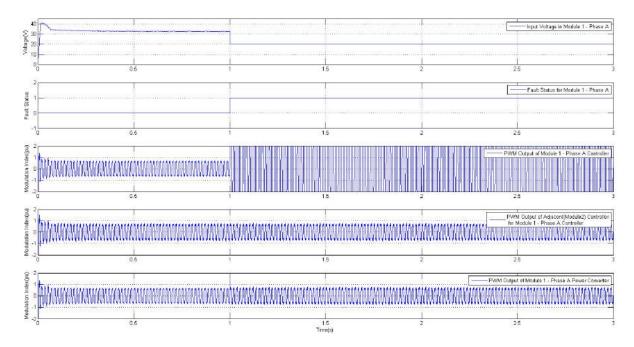

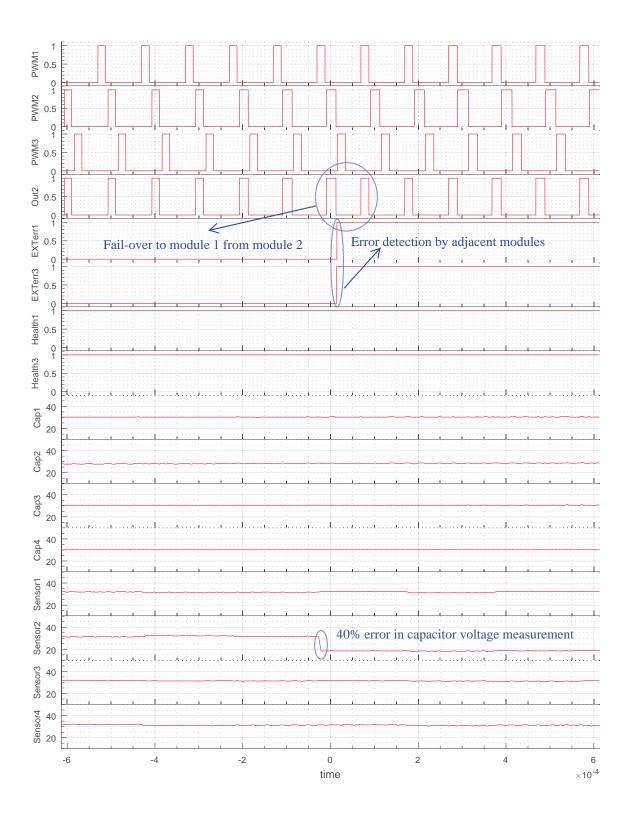

| Figure 3.36 | PWM Output of Main Controller and Adjacent Controller when Input Sensor                |    |

| c           | Failure Happens in Module 1(Phase A) at t=1s                                           | 89 |

| Figure 3.37 |                                                                                        |    |

| -           | in Module 1(Phase A) at t=1s                                                           | 90 |

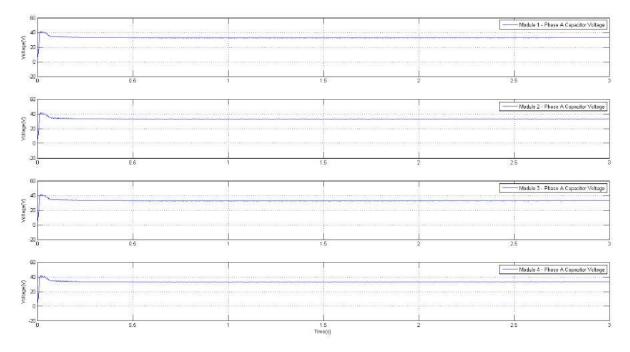

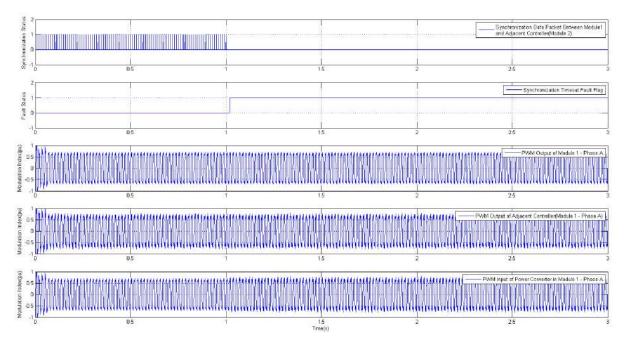

| Figure 3.38              | PWM Output of Main Controller and Adjacent Controller when Synchro-<br>nization Failure Happens in Module 1(Phase A) at t=1s                                         |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.39              | Module Capacitor Voltages for Phase A when Input Synchronization Failure<br>Happens in Module 1(Phase A) at t=1s                                                     |

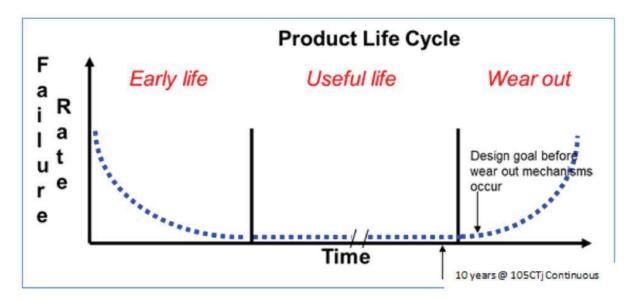

| Figure 4.1               | Bathtub Curving Showing Different Stage of Reliability                                                                                                               |

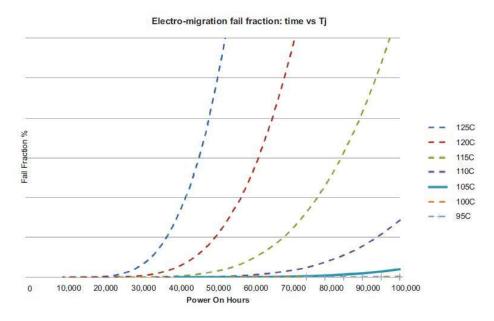

| Figure 4.2               | Impact of Temperature Increase on Embedded Processors (Texas Instrument) 96                                                                                          |

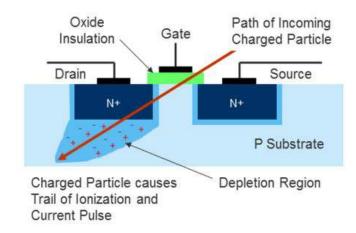

| Figure 4.3               | Local Ionization by Charged Particles (Space Radiation Associates) 97                                                                                                |

| Figure 4.4               | Effect of High-energy Particle Collision with MOSFET Transistor 98                                                                                                   |

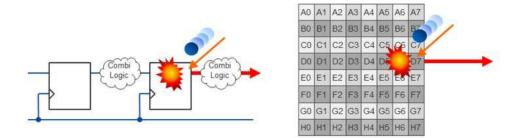

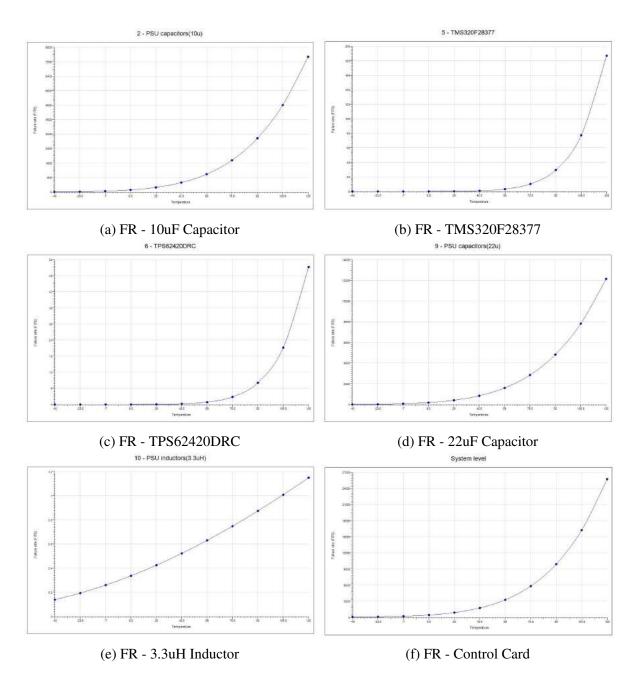

| Figure 4.5<br>Figure 4.6 | SEU Effect on SRAM-based Field Programmable Gate Array (FPGA) 99<br>Failure Rate (FR) Prediction for TI-F28377 Control Card over Temperature                         |

|                          | Range                                                                                                                                                                |

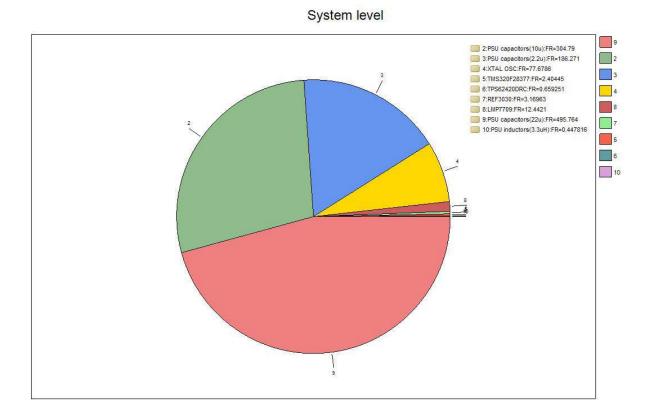

| Figure 4.7               | Portion of Failure Rate for each Component in Controller Card 105                                                                                                    |

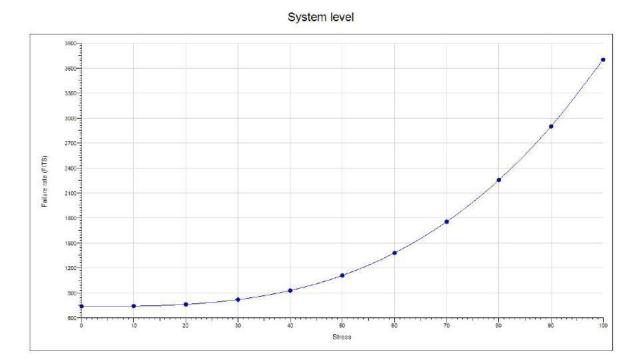

| Figure 4.8               | Failure Rate of Controller Card versus Stress                                                                                                                        |

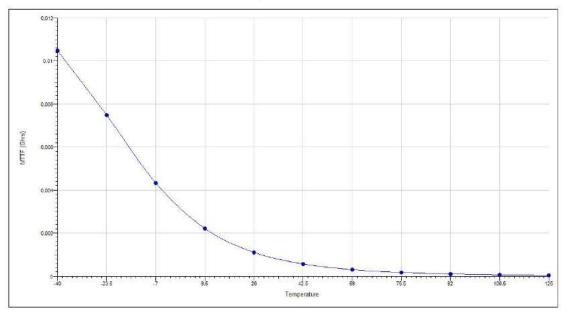

| Figure 4.9               | Mean Time to Failure of Controller Card versus Temperature                                                                                                           |

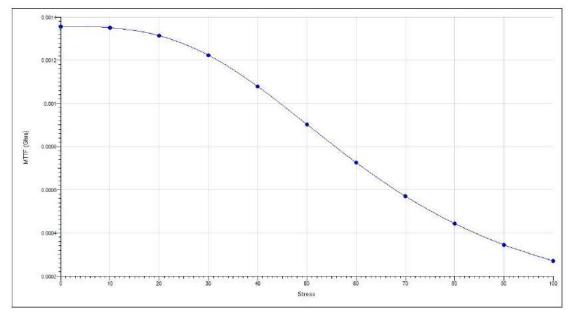

| Figure 4.10              | Mean Time to Failure of Controller Card versus Stress                                                                                                                |

| Figure 4.11              | Monte Carlo Simulation Result of the Proposed Controller with 4 Module                                                                                               |

|                          | per Leg and Failure Acceptance of 1 (n=1) with 100 steps and 1000000                                                                                                 |

|                          | iteration per step                                                                                                                                                   |

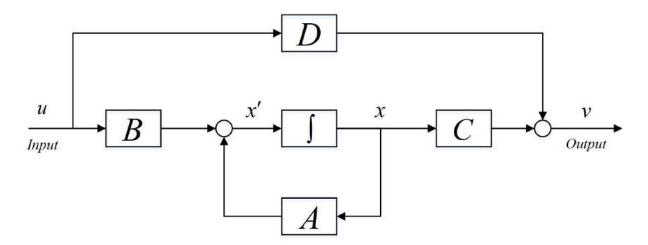

| Figure 4.12              | Block Diagram Representation of State-space Equations                                                                                                                |

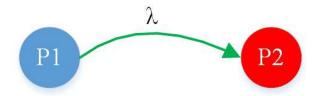

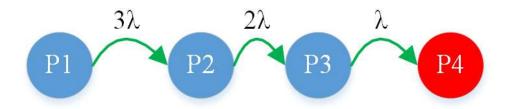

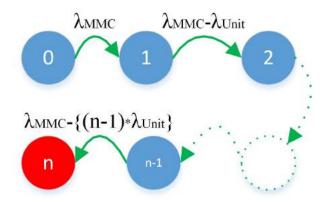

| Figure 4.13              | Markov Model of a Single Controller                                                                                                                                  |

| Figure 4.14              | Markov Model for Fault-tolerant Controllers                                                                                                                          |

| Figure 4.15              | Markov Model of Three-component Parallel Controller                                                                                                                  |

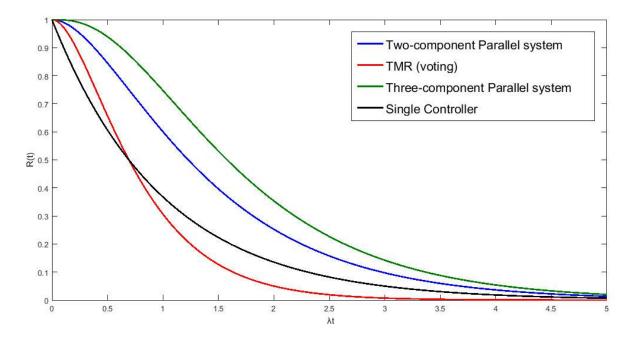

| Figure 4.16              | Reliability Assessment of Different Controller Architectures                                                                                                         |

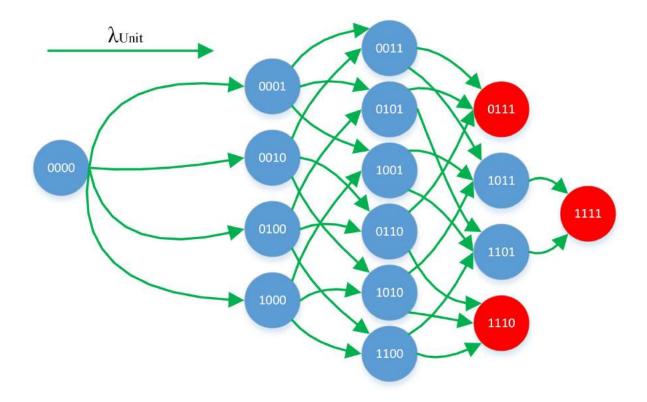

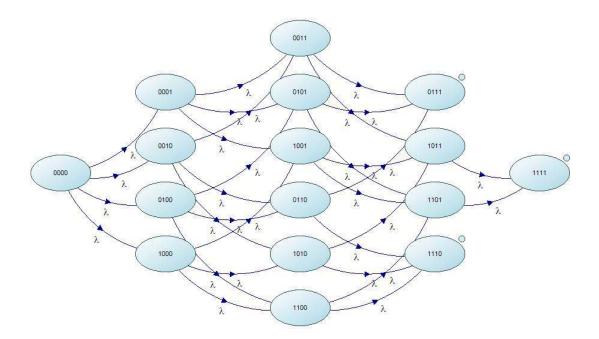

| Figure 4.17              | Markov Model of MMC with No Bypass Capability                                                                                                                        |

| Figure 4.18              | Markov Model of MMC with Bypass Capability                                                                                                                           |

| Figure 4.19              | Markov Model of MMC Controller (One Leg) with 4 Module per Leg and                                                                                                   |

| E                        | Failure Acceptance of 1 (n=1)123Provide Market Market Market Market Nuclear State125                                                                                 |

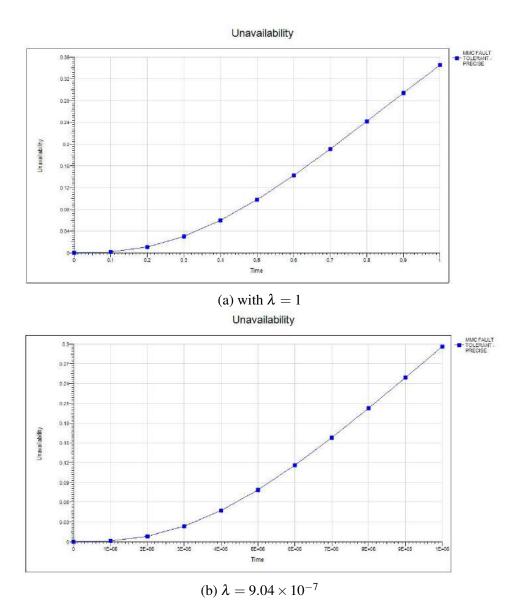

| -                        | Precise Markov Model of MMC Controller in RWB                                                                                                                        |

| Figure 4.21              |                                                                                                                                                                      |

| Eiguro 4 22              | per Leg and Failure Acceptance of 1 (n=1)                                                                                                                            |

| Figure 4.22              | Module per Leg and Failure Acceptance of $1 (n=1) \dots \dots$ |

|                          | Module per Leg and Fahure Acceptance of $1(n-1)$                                                                                                                     |

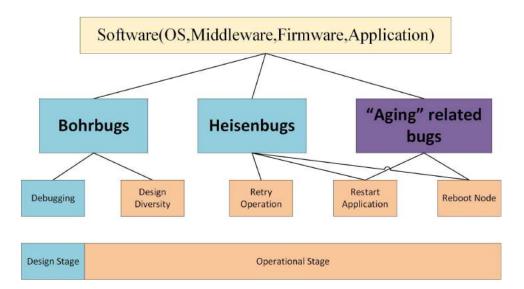

| Figure 5.1               | Classification of Software Fault Based on Gray Model                                                                                                                 |

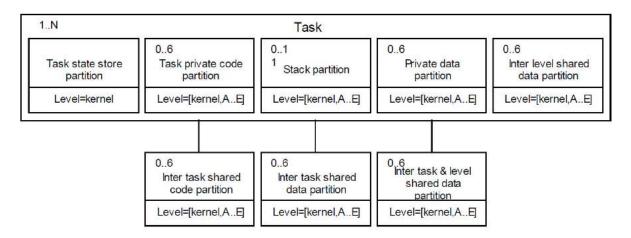

| Figure 5.2               | Architecture of Software Partitioning Based on Safety Levels                                                                                                         |

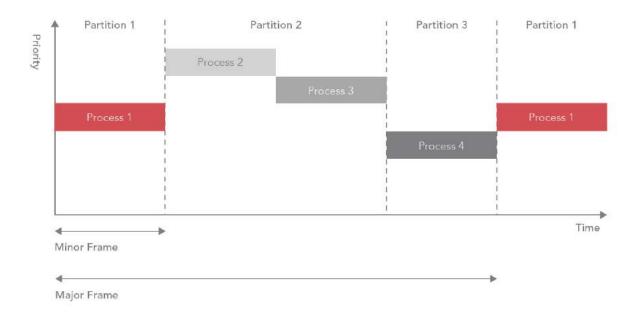

| Figure 5.3               | Temporal Partitioning in Reliable Systems                                                                                                                            |

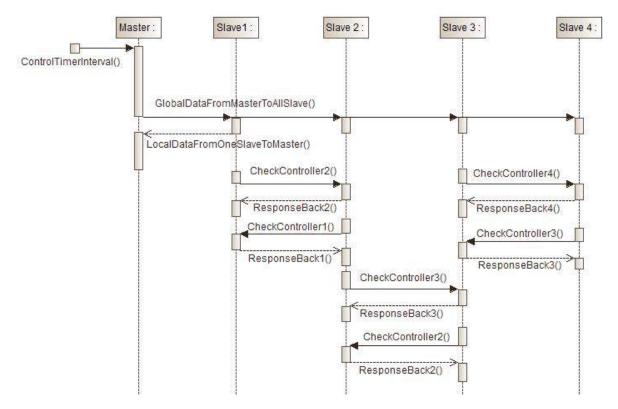

| Figure 5.4               | Sequence Diagram of Controller Interactions in First Generation Fault-                                                                                               |

|                          | tolerant Controller                                                                                                                                                  |

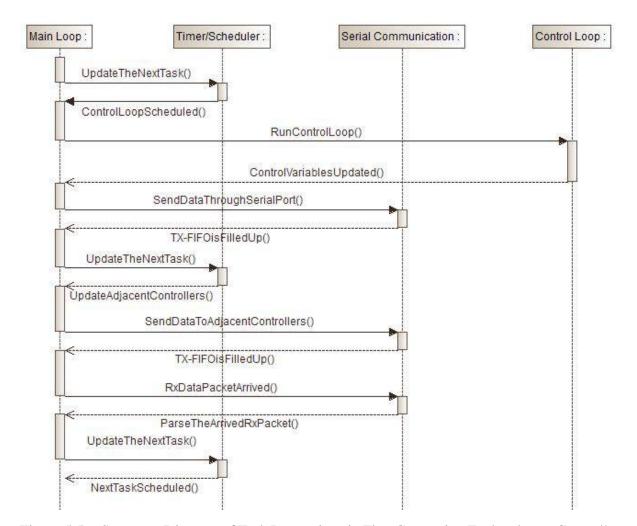

| Figure 5.5               | Sequence Diagram of Task Interactions in First Generation Fault-tolerant                                                                                             |

|                          | Controller                                                                                                                                                           |

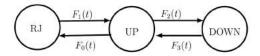

| Figure 5.6               | Rejuvenation Model for Fault-tolerant Controller                                                                                                                                                                                            |     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

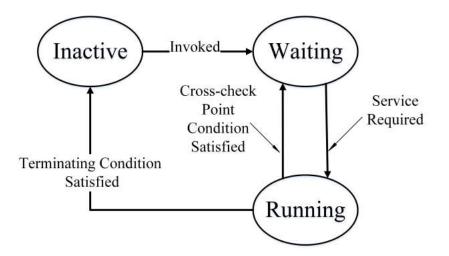

| Figure 5.7               | State Transition for Dynamic N-version Programming                                                                                                                                                                                          |     |

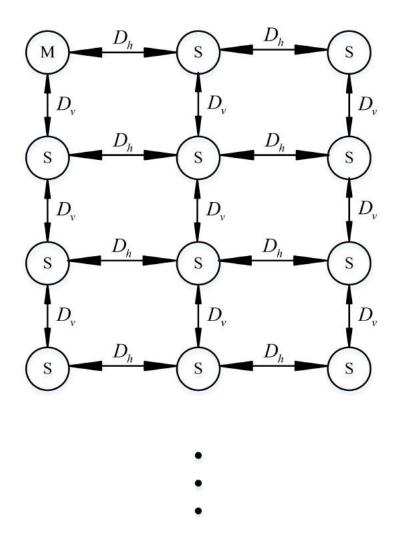

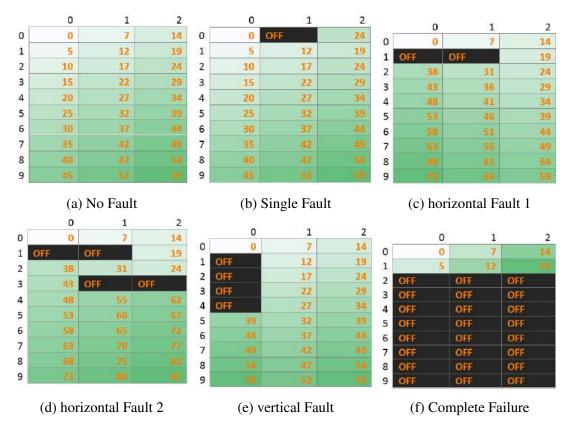

| Figure 5.8<br>Figure 5.9 | N-version Programming Implementation in Grid Synchronization 14<br>Simulation Result for General Agreement on the Master Controller (4 mod-<br>ule per phase, horizontal delay of 3, vertical delay of 2, maximum permitted<br>delay of 20) |     |

| Figure 5.10              | Simulation Result for General Agreement on the Master Controller (4 mod-<br>ule per phase, horizontal delay of 6, vertical delay of 5, maximum permitted<br>delay of 20)                                                                    |     |

|                          | • /                                                                                                                                                                                                                                         |     |

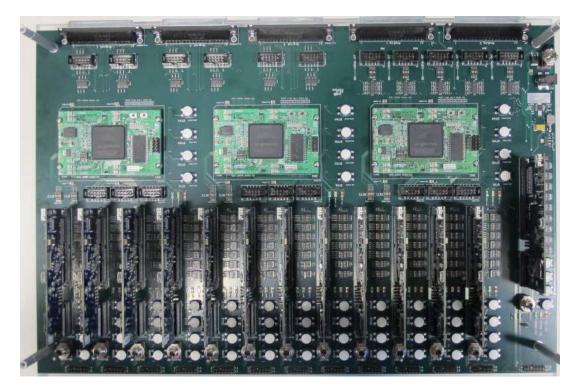

| Figure 6.1               | Fault-tolerant Controller Test-bed                                                                                                                                                                                                          |     |

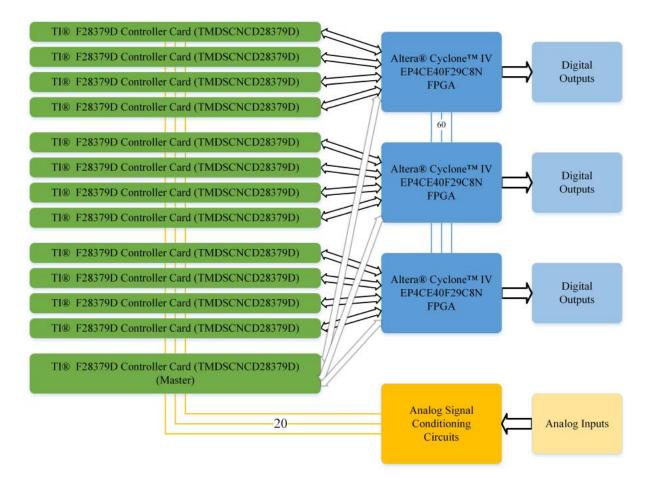

| Figure 6.2               | Block Diagram of Fault-tolerant Controller Test-bed                                                                                                                                                                                         |     |

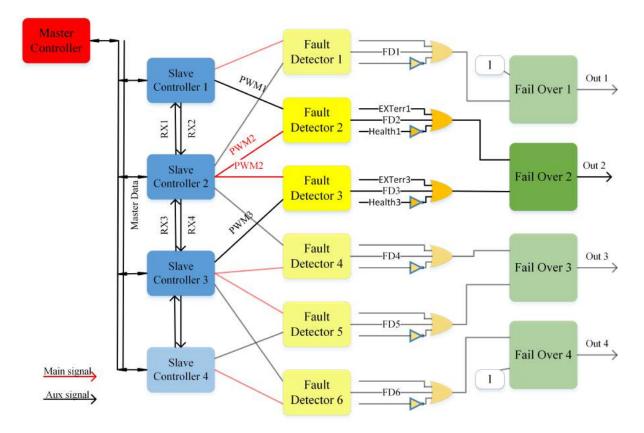

| Figure 6.3               | Fault Handling for each Phase (4 module per phase) of Converter 15                                                                                                                                                                          |     |

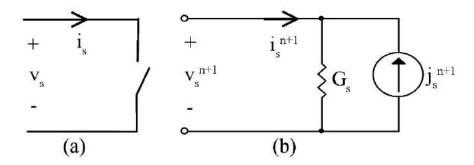

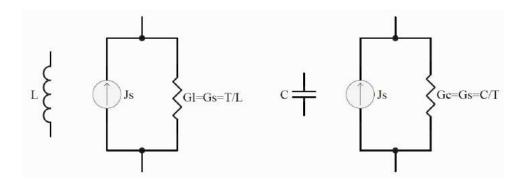

| Figure 6.4<br>Figure 6.5 | Simplified Model of Switch (a)Ideal Switch (b)Discrete-time Switch Model 15<br>Representation of the Pejovic Switch in On (inductor) and Off (capacitor)                                                                                    | 8   |

| 8                        | Mode                                                                                                                                                                                                                                        | 50  |

| Figure 6.6               | Fault-tolerant Controller in Connection with Opal-rt System (front view) 16                                                                                                                                                                 |     |

| Figure 6.7               | Fault-tolerant Controller in Connection with Opal-rt System (back view) 16                                                                                                                                                                  |     |

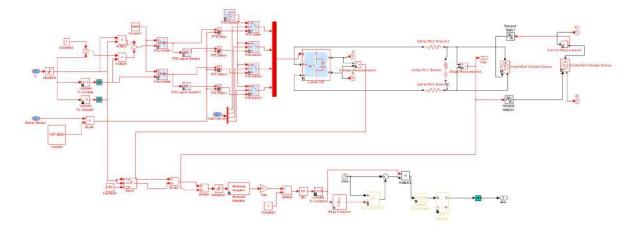

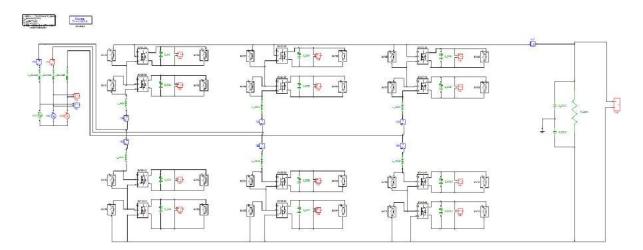

| Figure 6.8               | Implemented Cascaded H-bridge Converter with Isolated DC/DC Output                                                                                                                                                                          |     |

| C                        | Converter in Opal-rt HIL simulator                                                                                                                                                                                                          | 53  |

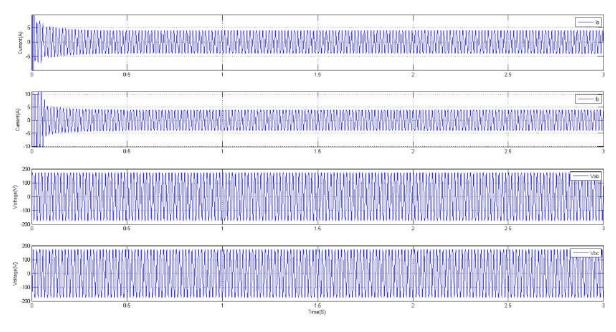

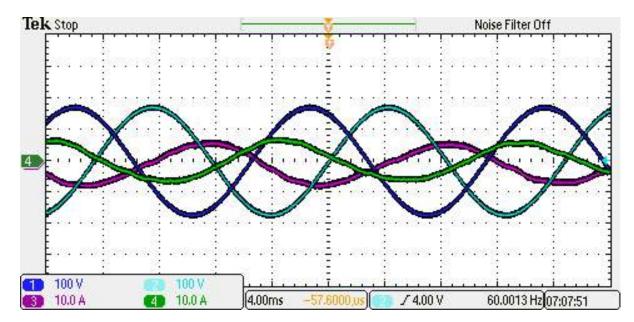

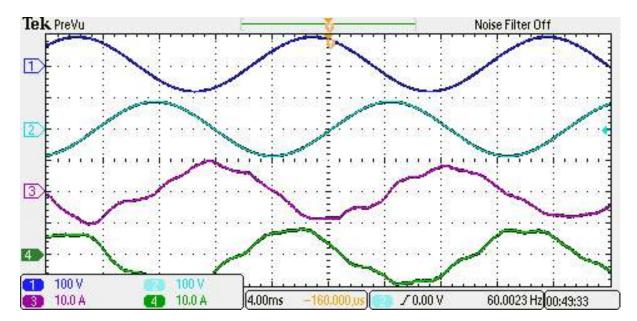

| Figure 6.9               | Grid Voltage and Current in Normal Operation of CHB (1:Vab 2:Vbc 3:Ia<br>4:Ib)                                                                                                                                                              |     |

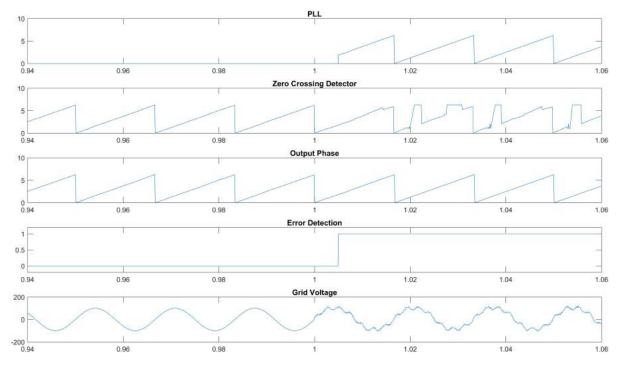

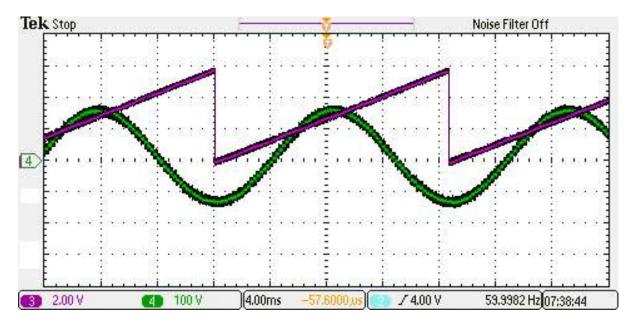

| Figure 6.10              | Synchronous Reference Frame PLL and Phase A Voltage (3:Phase(radian)                                                                                                                                                                        | 5   |

| I iguie 0.10             | 4:Phase A Voltage                                                                                                                                                                                                                           | 56  |

| Figure 6.11              | •                                                                                                                                                                                                                                           | 0   |

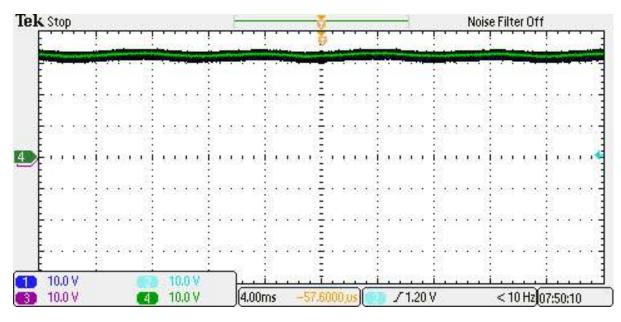

| I iguie 0.11             | ule 2 3:Module 3 4:Module 4)                                                                                                                                                                                                                | 6   |

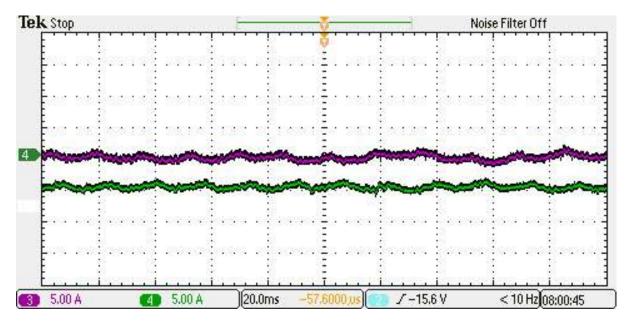

| Figure 6.12              | Active and Reactive Current in Normal Operation (3:Reactive Current 4:Ac-                                                                                                                                                                   | 0   |

| 1 iguie 0.12             | tive Current)                                                                                                                                                                                                                               | 57  |

| Figure 6.13              | PWM Reference Signals for Phase A and B in Normal Operation (3:Phase                                                                                                                                                                        |     |

| 1.8010 0110              | A 4:Phase B)                                                                                                                                                                                                                                | 57  |

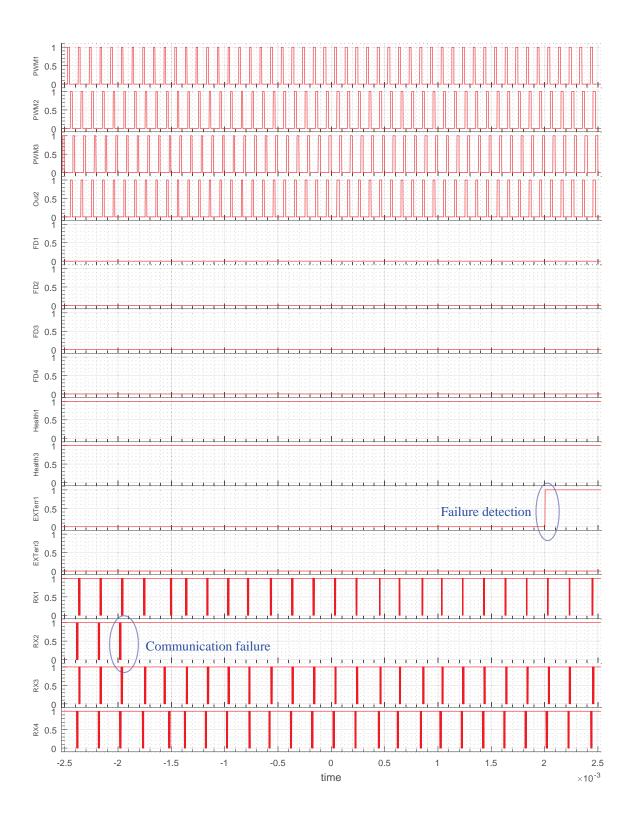

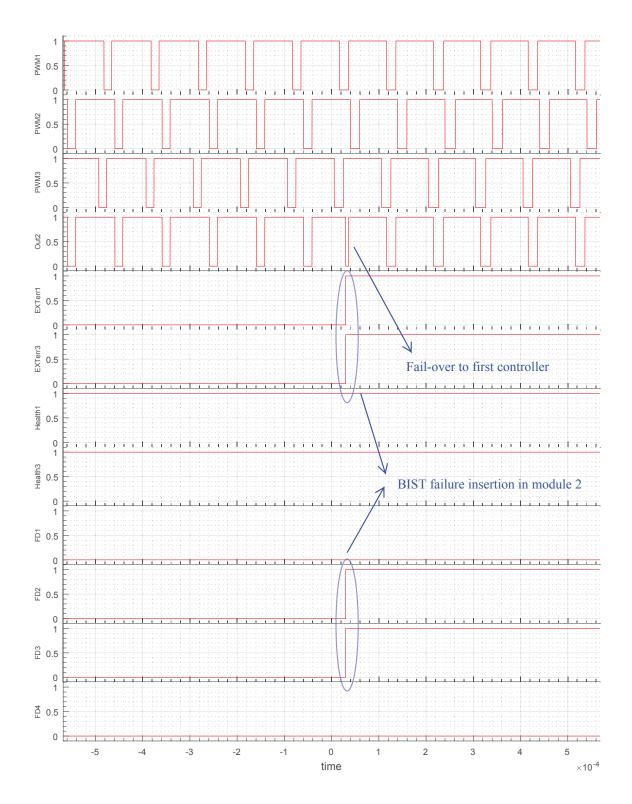

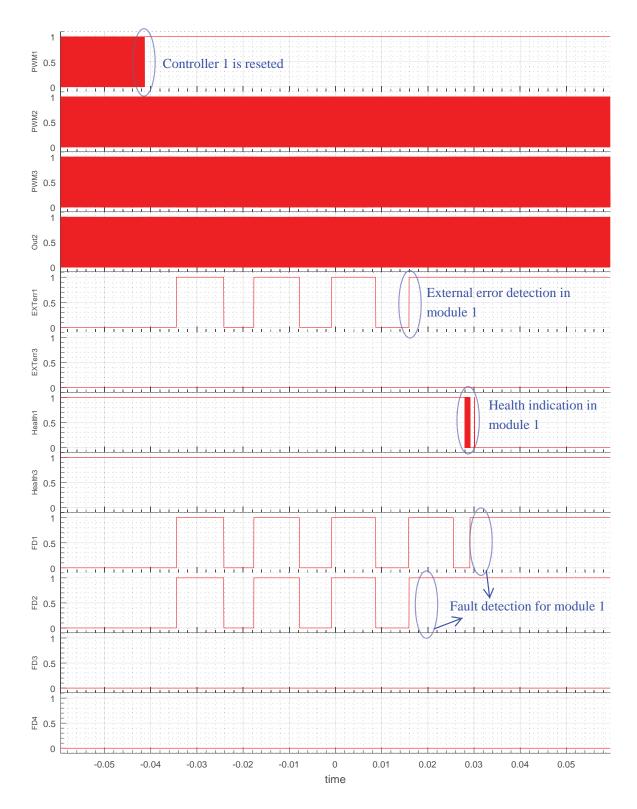

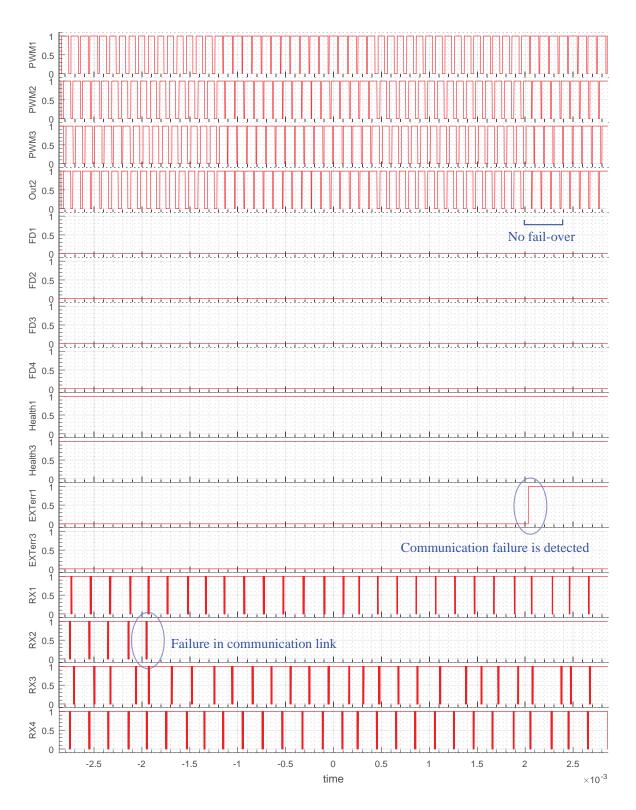

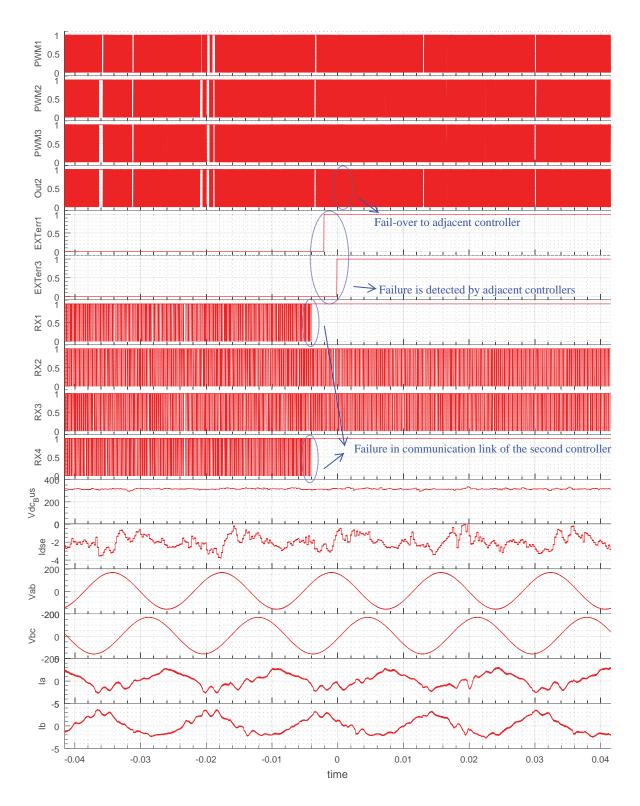

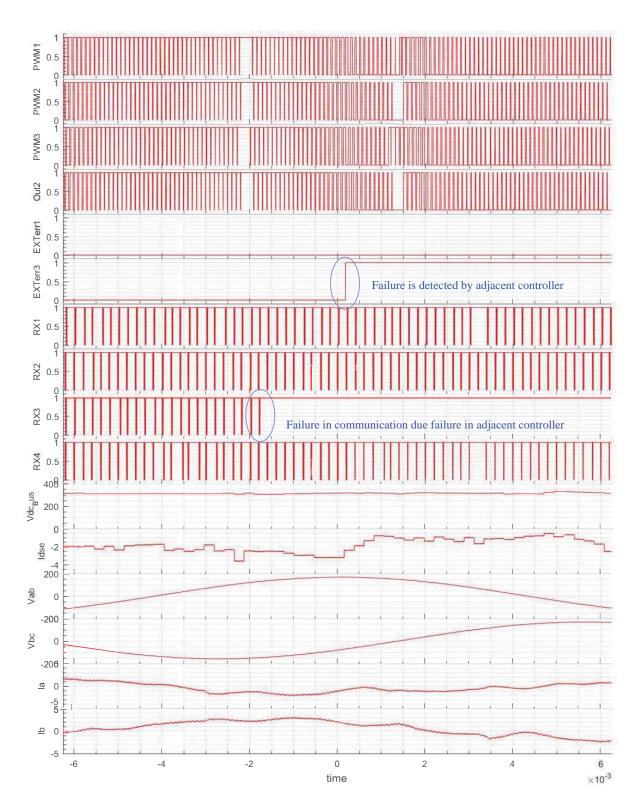

| Figure 6.14              | Communication Failure in Module 1 and Its Effect on Module 2 in CHB 17                                                                                                                                                                      |     |

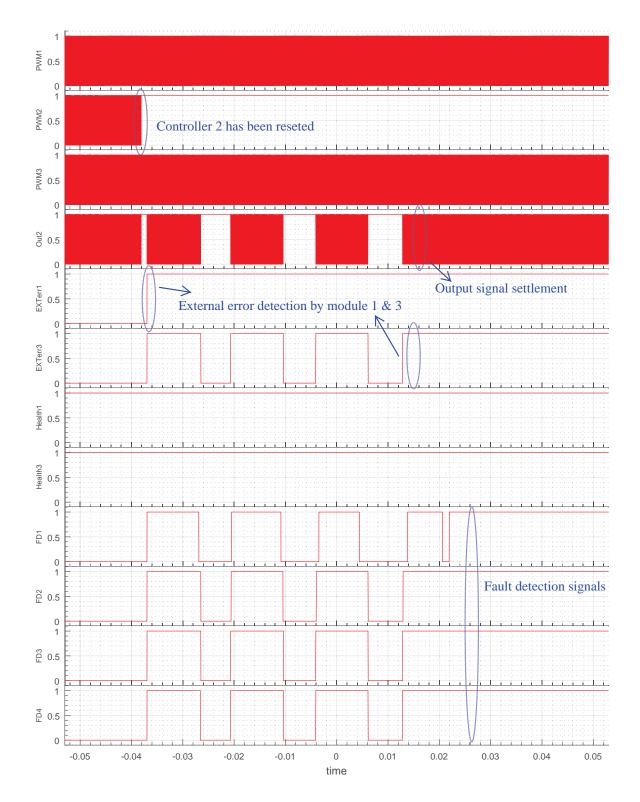

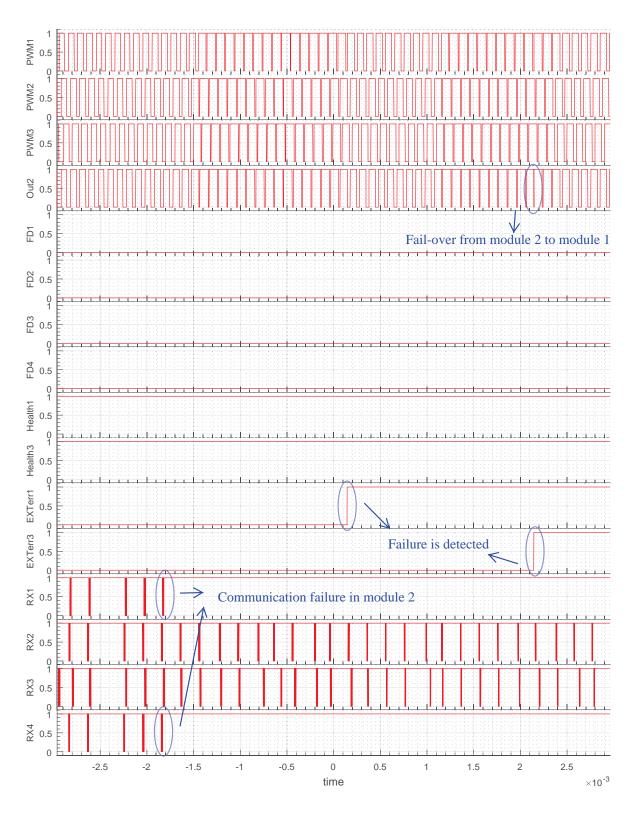

| -                        | Communication Failure in Module 2 and Its Effect on Module 2 in CHB 17                                                                                                                                                                      |     |

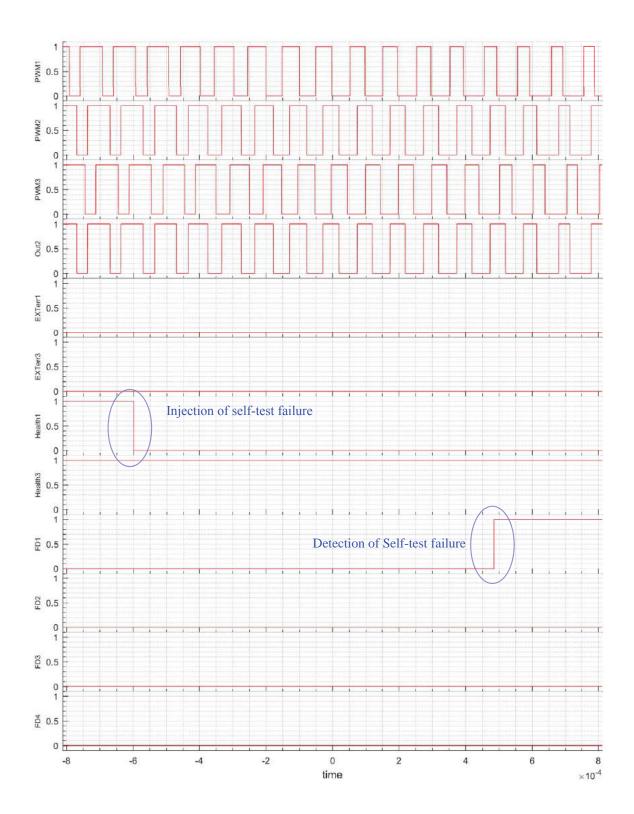

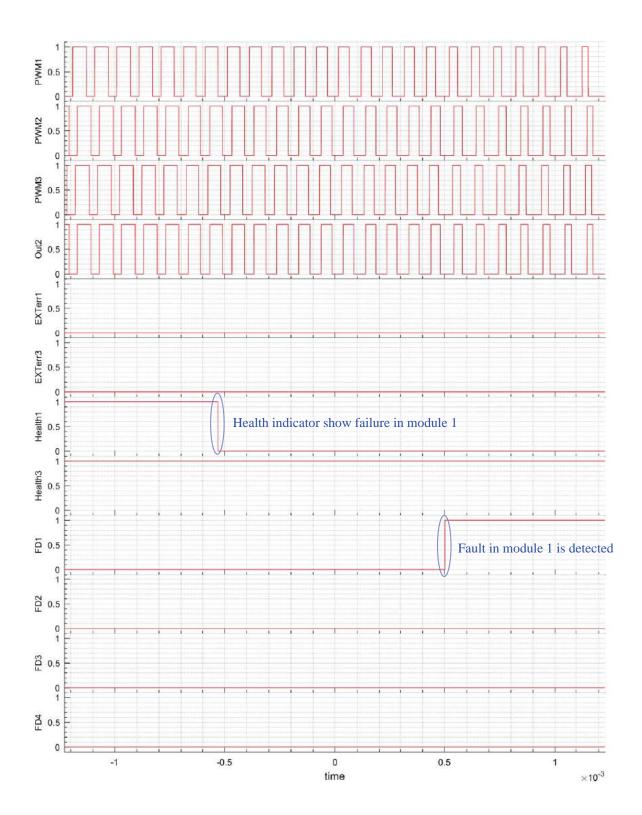

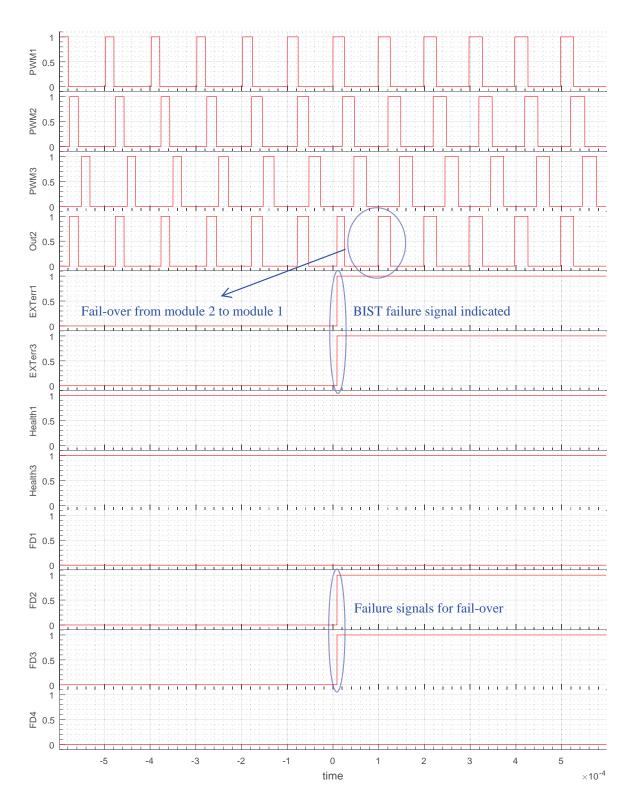

| -                        | Built In Self-test (BIST) Failure in Module 1 and Its Effect on Module 2 in                                                                                                                                                                 |     |

| U                        | СНВ                                                                                                                                                                                                                                         | '4  |

| Figure 6.17              | Built In Self-test (BIST) Failure in Module 2 and Its Effect on Module 2 in                                                                                                                                                                 | . – |

| <b>D'</b> (10)           | CHB                                                                                                                                                                                                                                         |     |

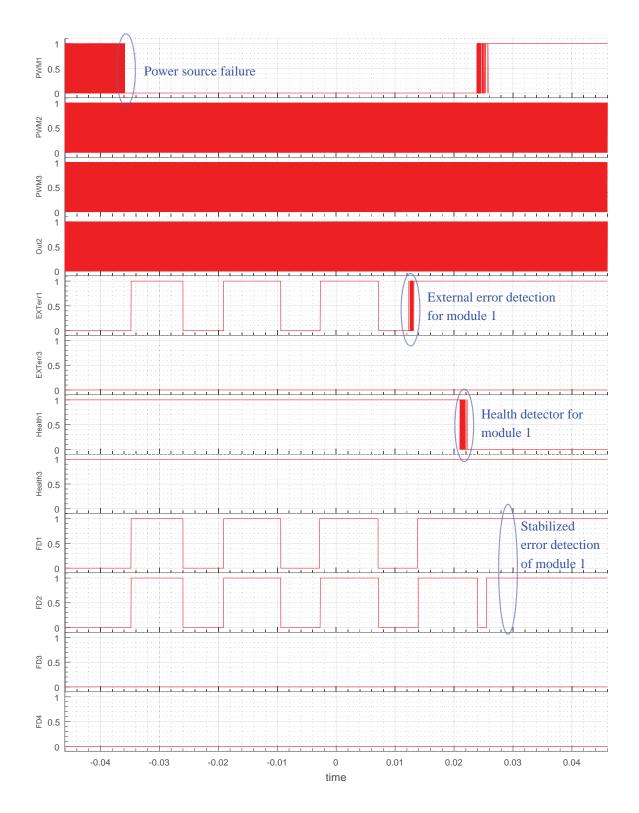

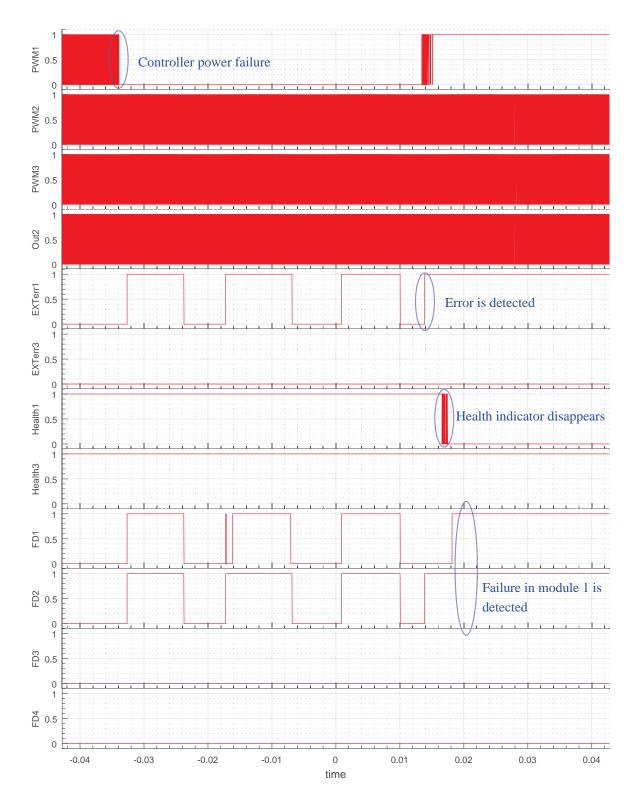

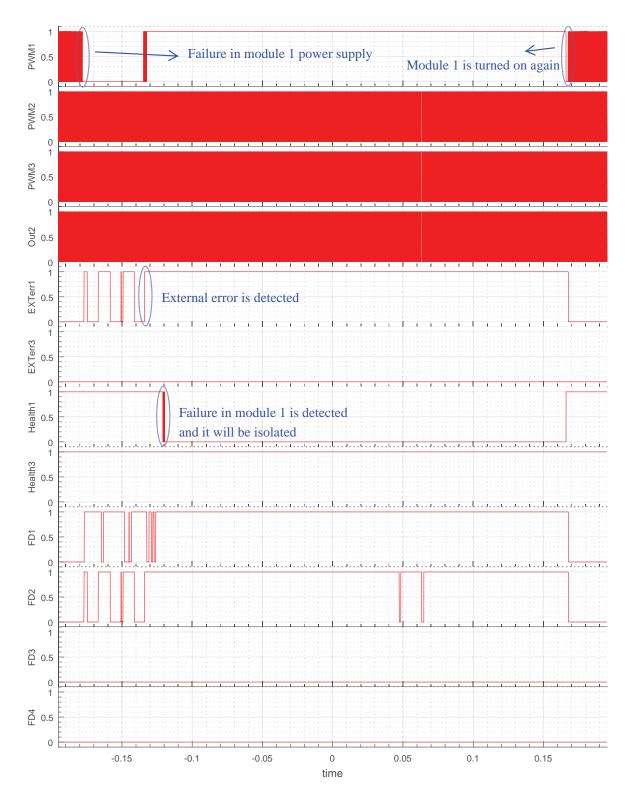

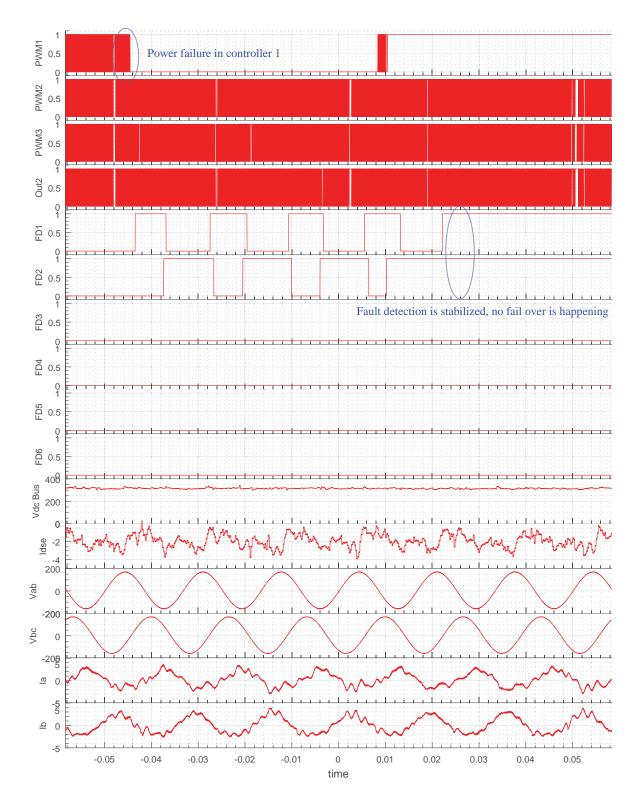

| -                        | Power Failure in Module 1 and Its effect on Module 2 in CHB                                                                                                                                                                                 |     |

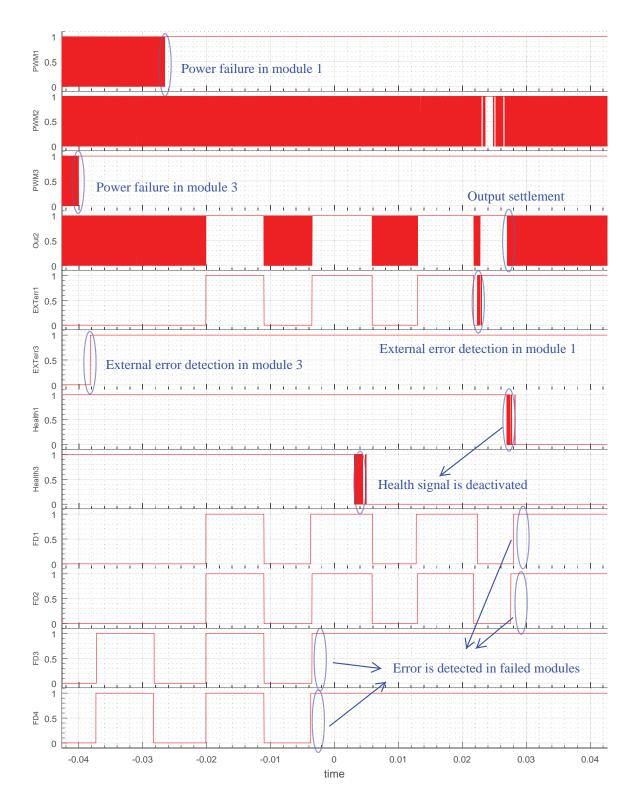

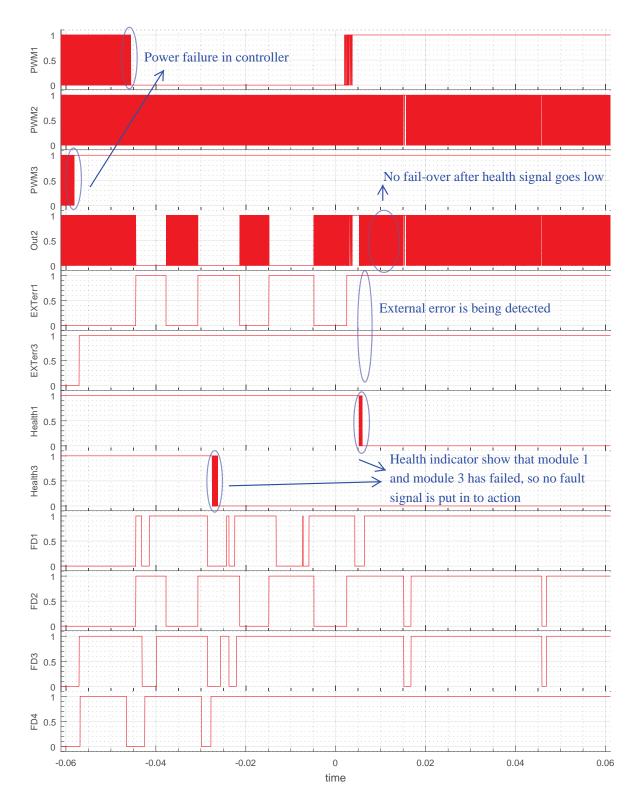

| e                        | Power Failure in Module 1 and Module 3 and Its effect on Module 2 in CHB 17                                                                                                                                                                 |     |

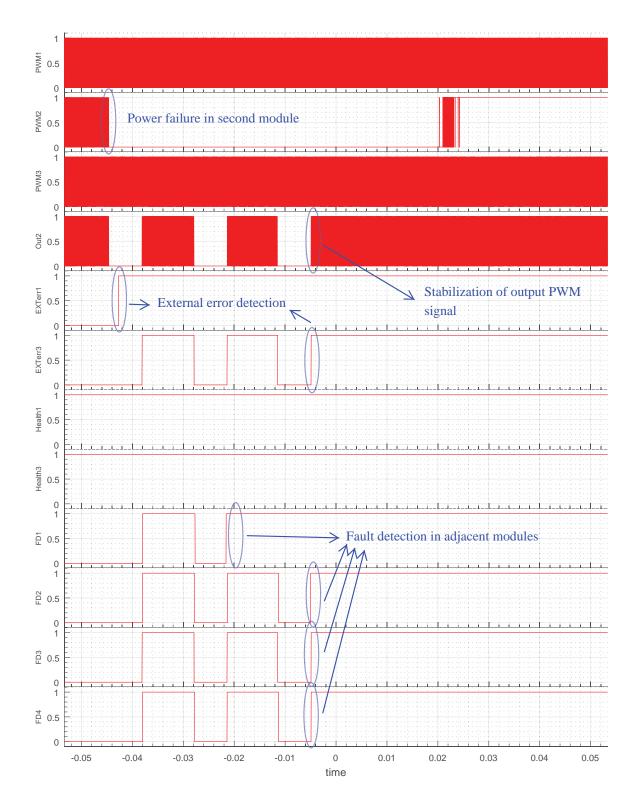

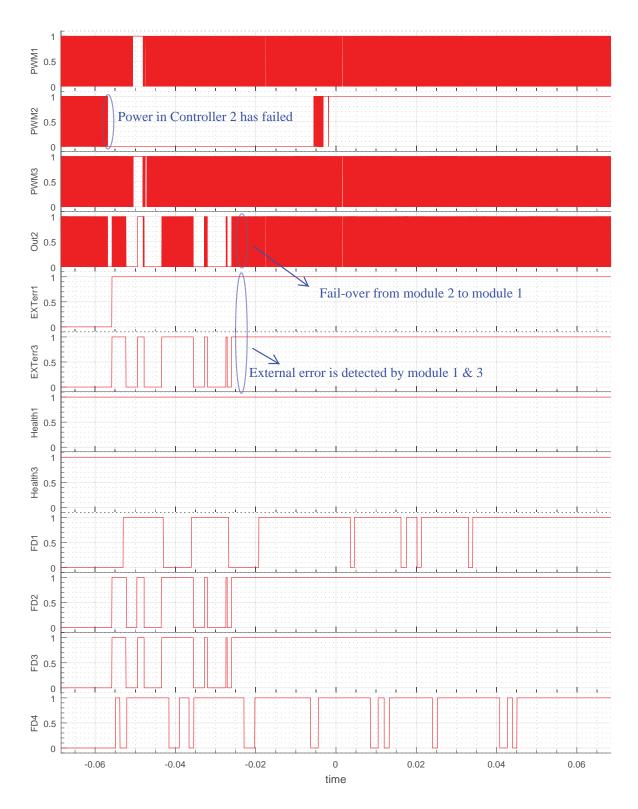

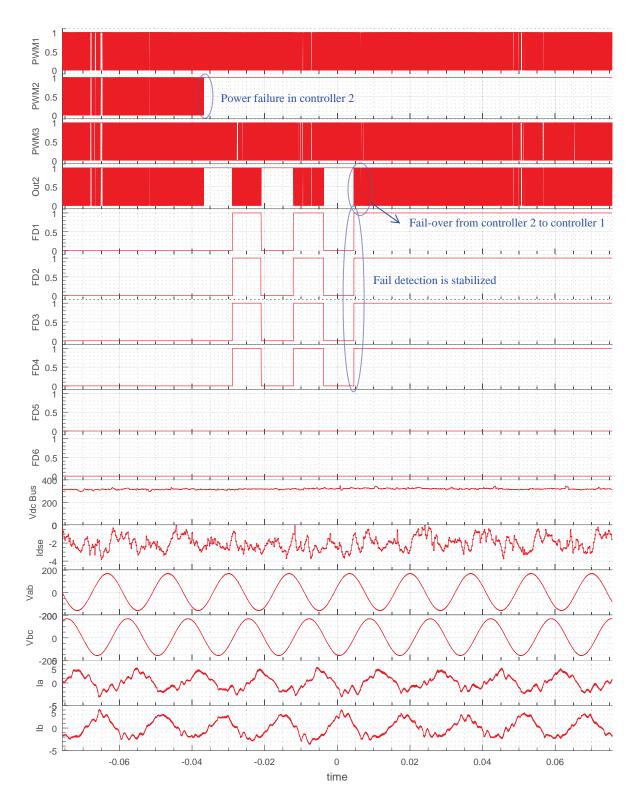

| e                        | Power Failure in Module 2 and Its effect on Module 2 in CHB                                                                                                                                                                                 |     |

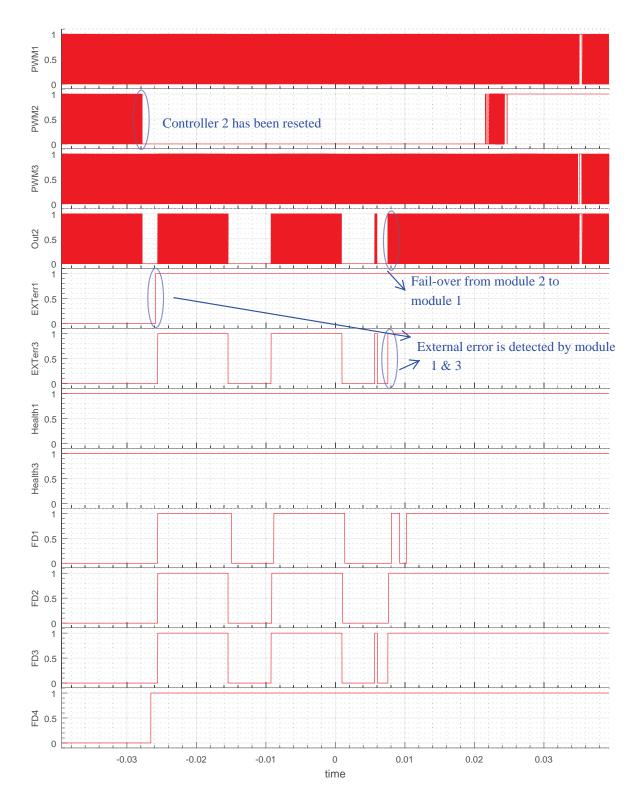

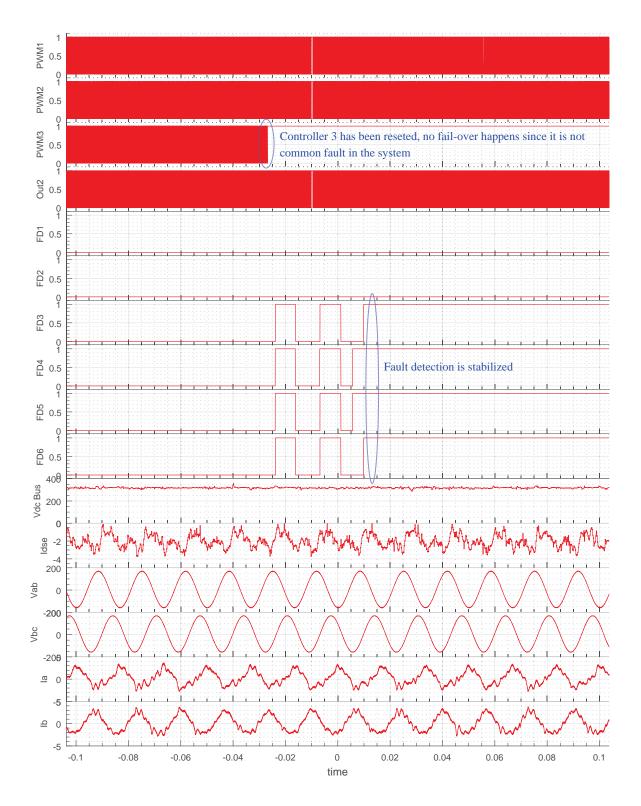

| e                        | Micro-controller Reset in Module 1 and Its effect on Module 2 in CHB 17                                                                                                                                                                     |     |

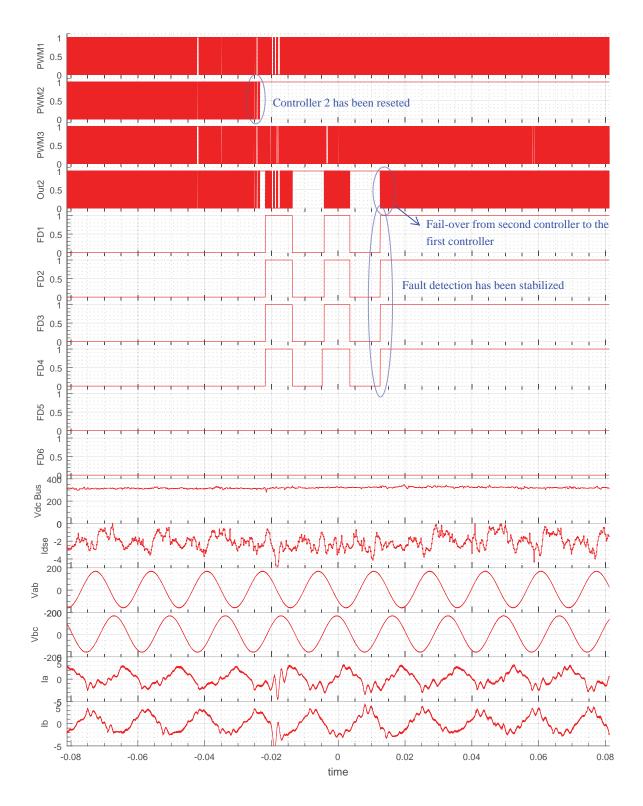

| Figure 6.22              | Micro-controller Reset in Module 2 and Its effect on Module 2 in CHB 18                                                                                                                                                                     | 50  |

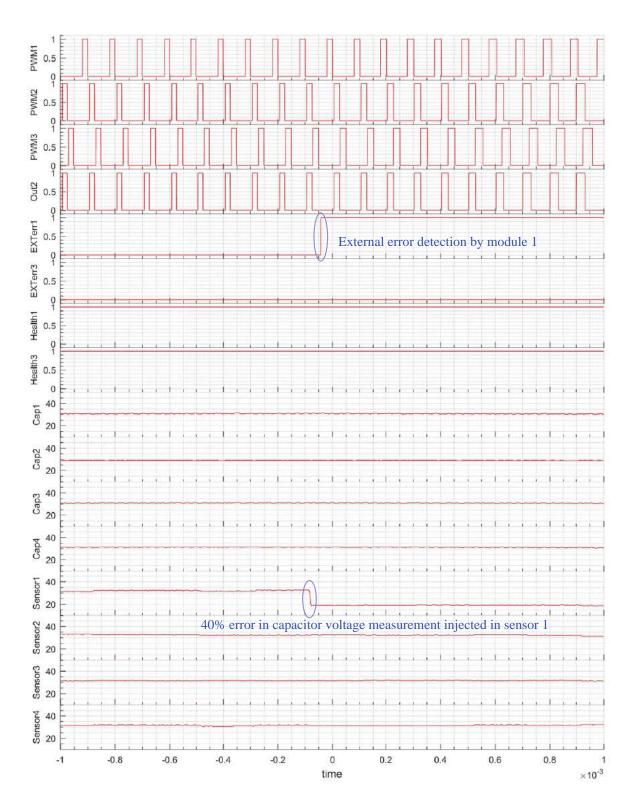

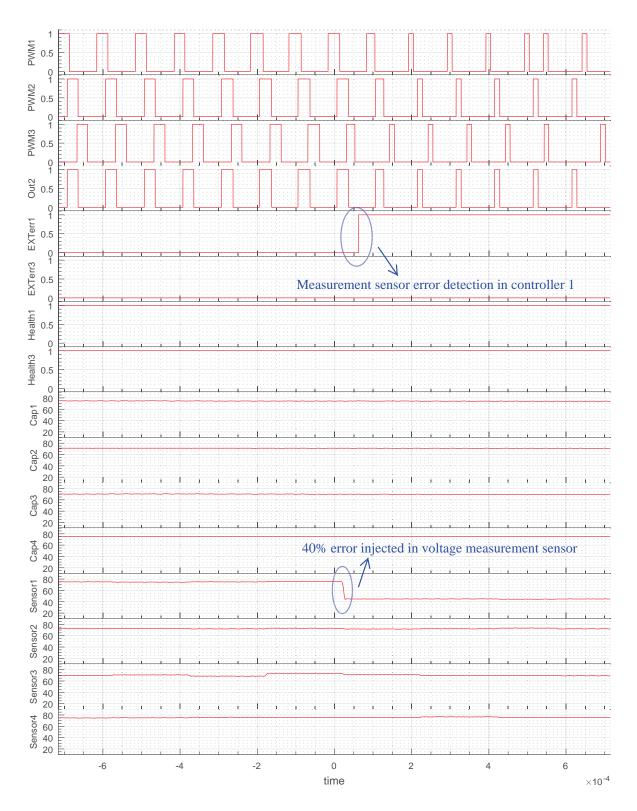

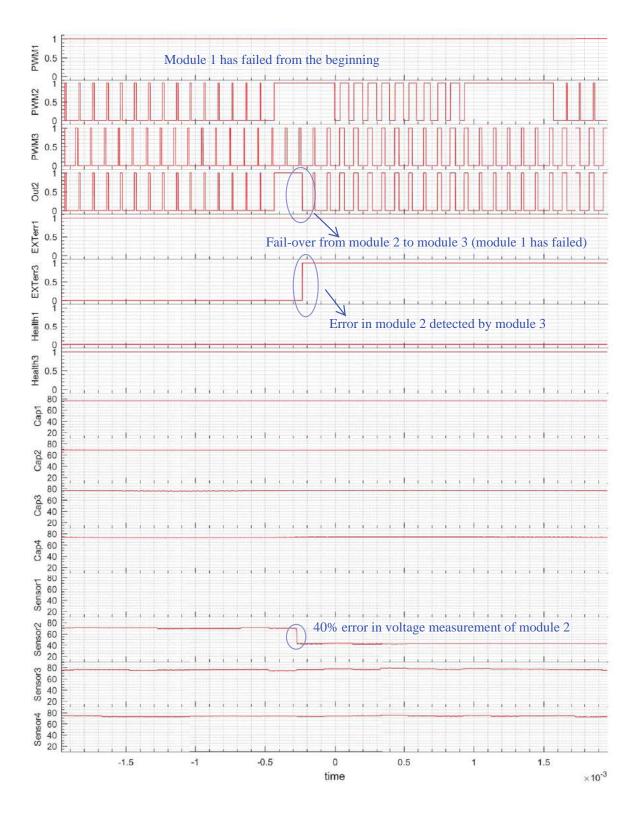

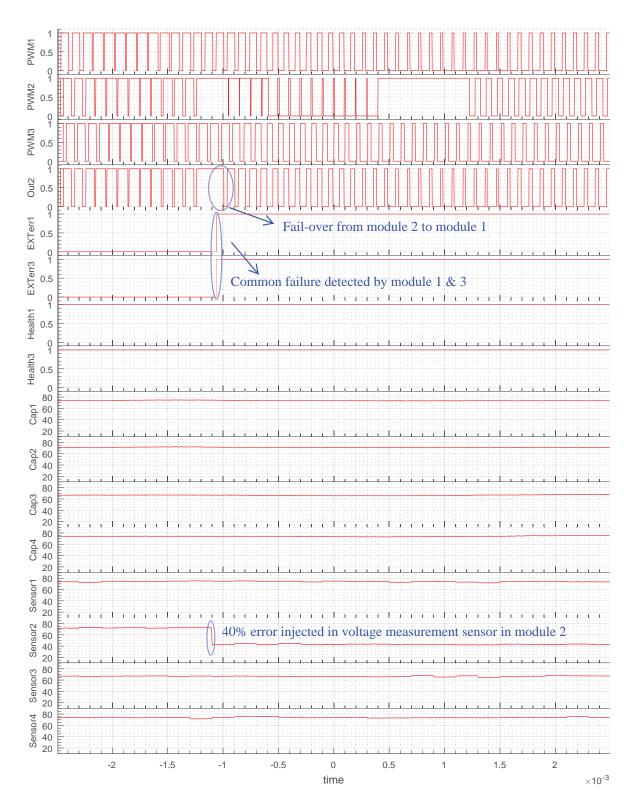

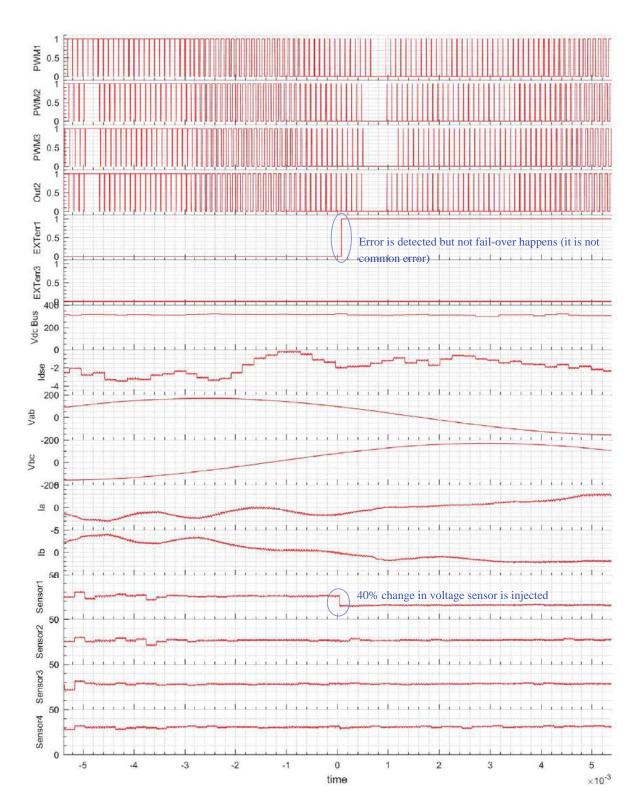

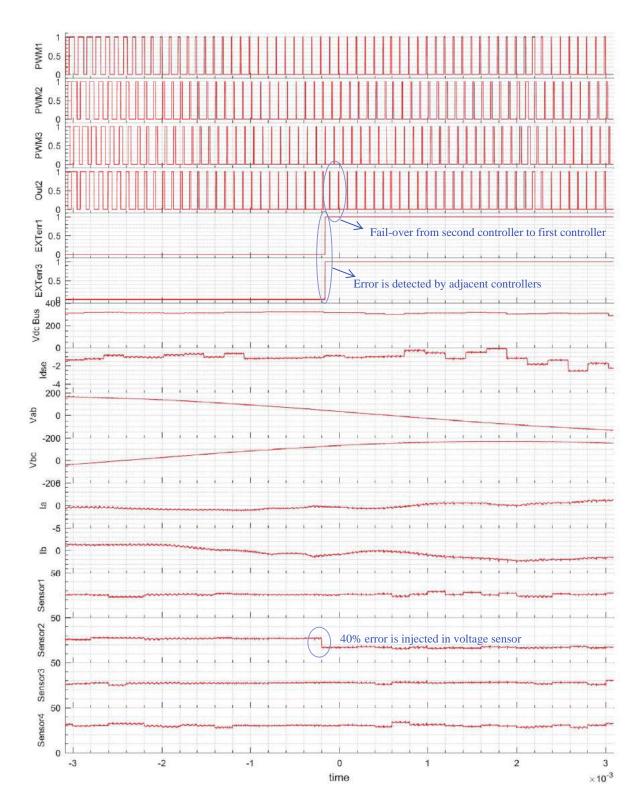

| Figure 6.23 | Voltage Sensor Failure in Module 1 and Its effect on Module 2 in CHB 181    |

|-------------|-----------------------------------------------------------------------------|

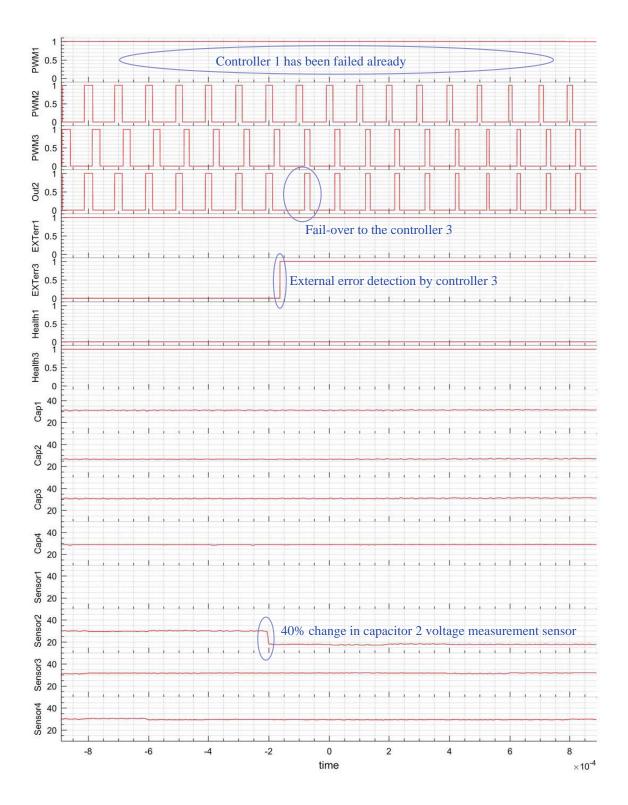

| Figure 6.24 | Voltage Sensor Failure in Module 3 While Module 1 has failed and Its effect |

| -           | on Module 2 in CHB                                                          |

| Figure 6.25 | Voltage Sensor Failure in Module 2 and Its effect on Module 2 in CHB 183    |

| Figure 6.26 | Capacitor Voltage in each Module at the Time of Failure in Power Electronic |

|             | Circuit (Power Module Bypassed)                                             |

| Figure 6.27 | Average Capacitor Voltages in each Phase of the Converter at the Time of    |

|             | Failure in Power Electronic Circuit (Power Module Bypassed)                 |

| Figure 6.28 | Grid Voltages and Currents at the Time of Failure in Power Electronic       |

|             | Circuit (Power Module Bypassed)                                             |

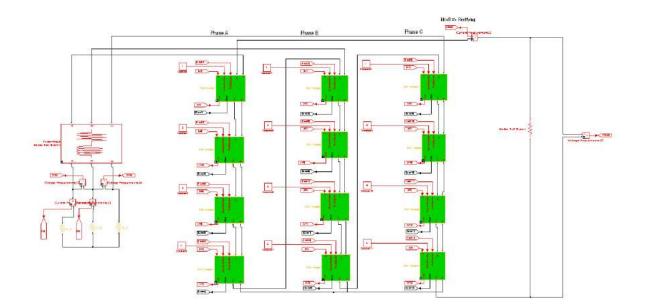

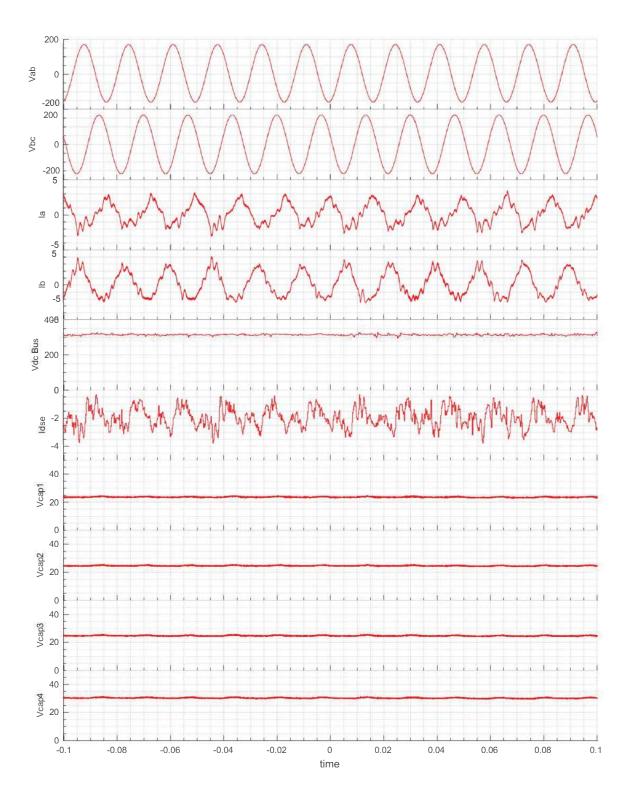

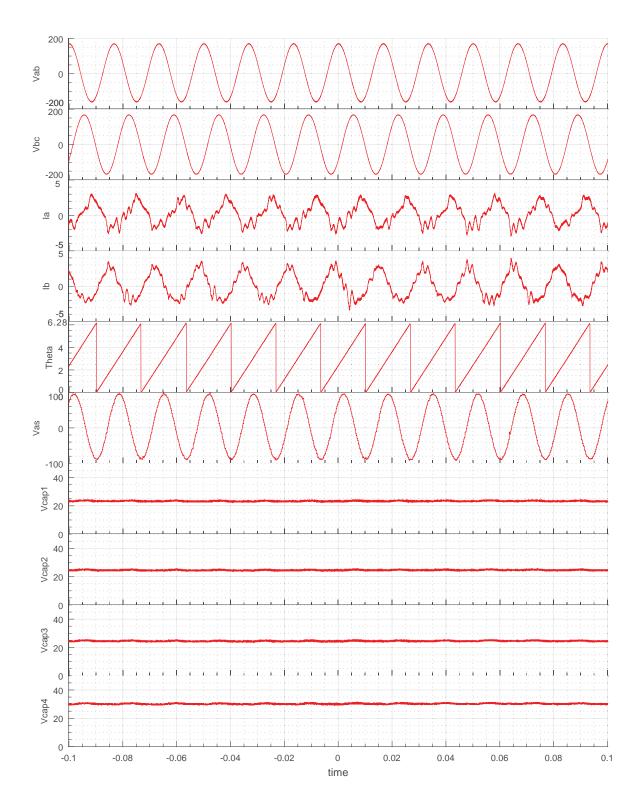

| Figure 6.29 | Implemented Modular Multi-level Converter (MMC) in Opal-rt HIL simulator186 |

| Figure 6.30 | Grid Voltage and Current in Normal Operation of MMC (1:Vab 2:Vbc 3:Ia       |

|             | 4:Ib)                                                                       |

| Figure 6.31 | Synchronous Reference Frame PLL and Phase A Voltage (1:Phase (radian)       |

|             | 2:Phase A Voltage                                                           |

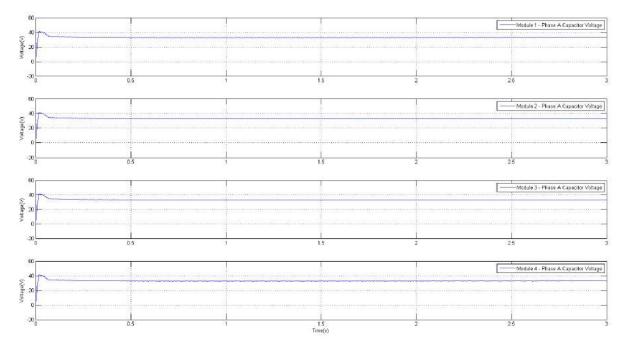

| Figure 6.32 | Capacitor Voltage of each Module in Normal Operation (1:Module 1 2:Mod-     |

|             | ule 2 3:Module 3 4:Module 4)                                                |

| Figure 6.33 | Active and Reactive Current in Normal Operation (1:Active Current 2:Reac-   |

|             | tive Current)                                                               |

| Figure 6.34 |                                                                             |

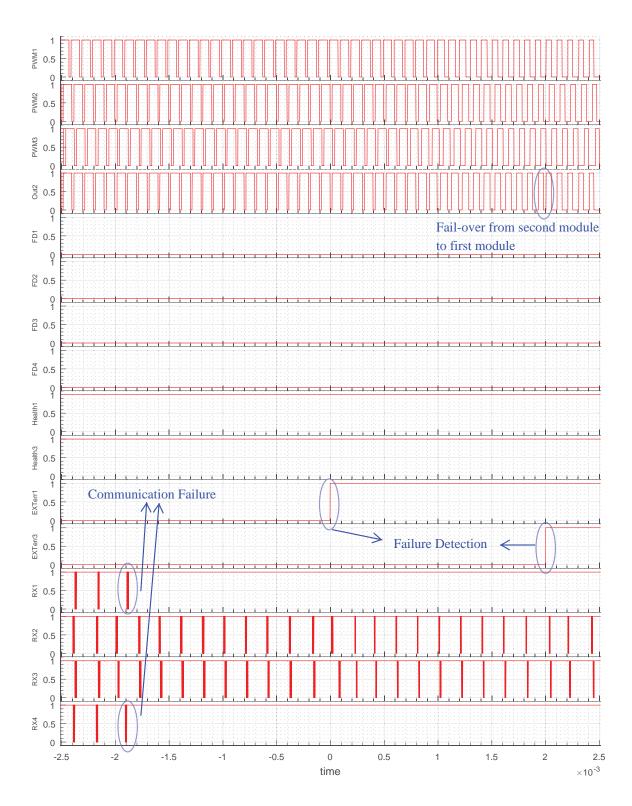

| •           | Communication Failure in Module 2 and Its Effect on Module 2 in MMC . 195   |

| Figure 6.36 | Built In Self-test (BIST) Failure in Module 1 and Its Effect on Module 2 in |

|             | MMC                                                                         |

| Figure 6.37 | Built In Self-test (BIST) Failure in Module 2 and Its Effect on Module 2 in |

|             | MMC                                                                         |

| U           | Power Failure in Module 1 and Its effect on Module 2 in MMC                 |

| Figure 6.39 |                                                                             |

| Figure 6.40 | Power Failure in Module 2 and Its effect on Module 2 in MMC 200             |

| Figure 6.41 | Micro-controller Reset in Module 1 and Its effect on Module 2 in MMC 201    |

| Figure 6.42 | Micro-controller Reset in Module 2 and Its effect on Module 2 in MMC 202    |

| Figure 6.43 | Voltage Sensor Failure in Module 1 and Its effect on Module 2 in MMC 203    |

| Figure 6.44 | Voltage Sensor Failure in Module 3 While Module 1 has failed and Its effect |

|             | on Module 2 in MMC                                                          |

| -           | Voltage Sensor Failure in Module 2 and Its effect on Module 2 in MMC 205    |

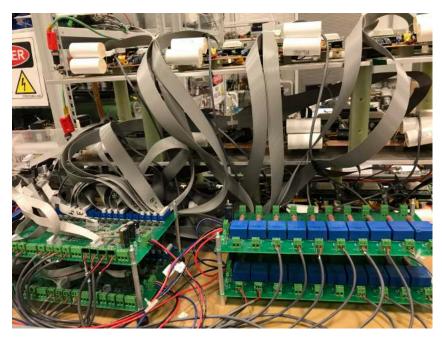

| Figure 6.46 | Experimental Setup of Cascaded H-bridge Converter (CHB) in Connection       |

|             | with Fault-tolerant Controller                                              |

| e           | Side View of Cascaded H-bridge Converter (CHB)                              |

| Figure 6.48 | Interconnection Between Interface Card, Measurement Board and Cascaded      |

|             | H-bridge Converter (CHB)                                                    |

| Figure 6.49 | Voltage Measurement Board in CHB Setup                                      |

| Figure 6.50   | Interface Board in CHB Setup                                                | 8 |

|---------------|-----------------------------------------------------------------------------|---|

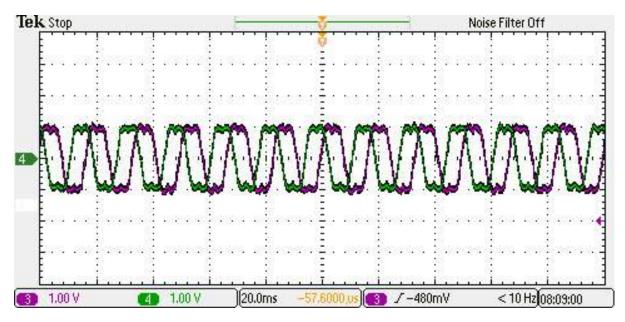

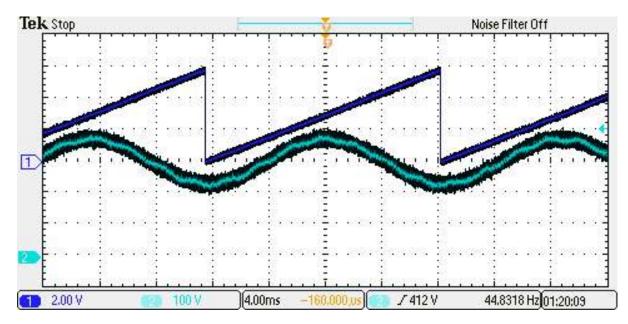

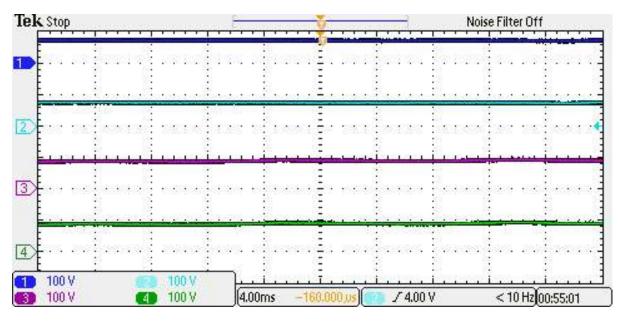

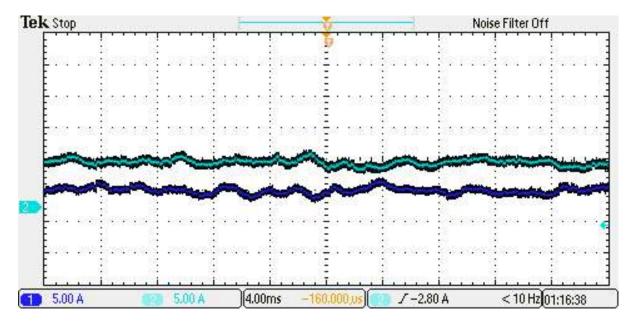

| -             | CHB in Normal Operation (DC Bus Voltage and Reactive Current are Shown)21   |   |

| Figure 6.52   | CHB in Normal Operation (PLL Output is Shown)                               | 2 |

| Figure 6.53   | Experimental Result of Communication Failure in Controller 2 and its Effect |   |

|               | on the System                                                               | 3 |

| Figure 6.54   | Experimental Result of Communication Failure in Controller 3 and its Effect |   |

|               | on the System                                                               | 4 |

| Figure 6.55   | Experimental Result of Power Supply Failure in Controller 1 and its Effect  |   |

|               | on the System                                                               | 5 |

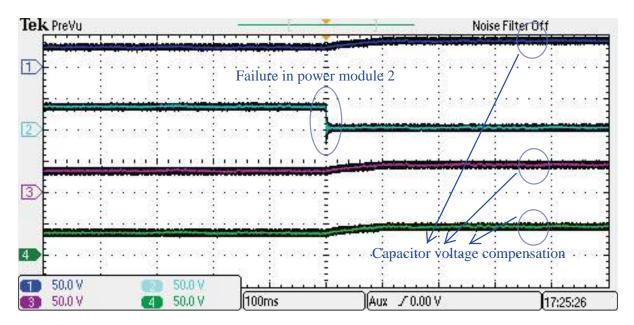

| Figure 6.56   | Experimental Result of Power Supply Failure in Controller 2 and its Effect  |   |

| -             | on the System                                                               | 6 |

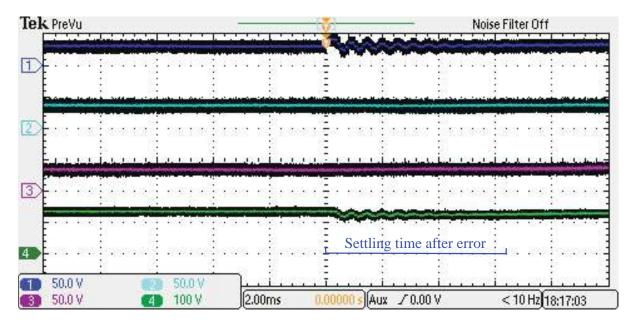

| Figure 6.57   | Experimental Result of Microprocessor Reset in Controller 3 and its Effect  |   |

|               | on the System                                                               | 7 |

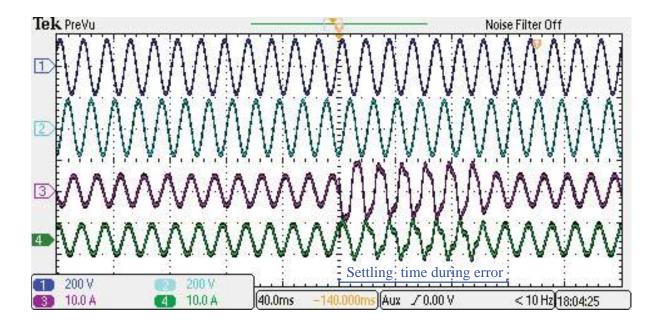

| Figure 6.58   | Experimental Result of Microprocessor Reset in Controller 2 and its Effect  |   |

|               | on the System                                                               | 8 |

| Figure 6.59   | Experimental Result of Voltage Measurement Sensor Failure in Controller 1   |   |

|               | and its Effect on the System                                                | 9 |

| Figure 6.60   | Experimental Result of Voltage Measurement Sensor Failure in Controller 2   |   |

|               | and its Effect on the System                                                | 0 |

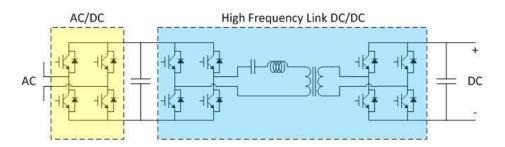

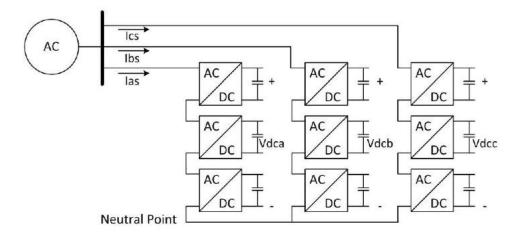

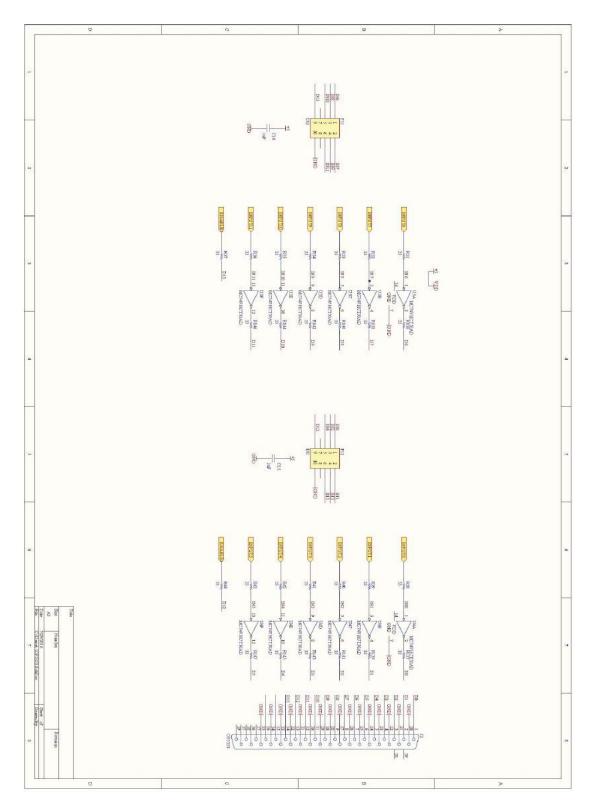

| Figure A.1    | Cascaded H-bridge Multi-level Converter with Isolated Output Stage 234      | 4 |

| Figure A.2    | Detailed Schematic of Converter Modules in Cascaded H-bridge Multi-level    | • |

| 1 19010 1 1.2 | Converter                                                                   | 4 |

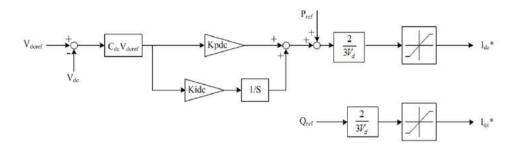

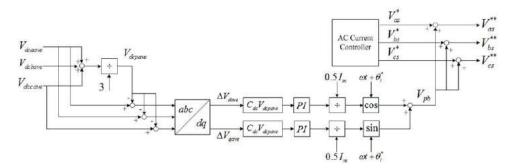

| Figure A.3    | DC Grid Voltage Controller for the Converter                                |   |

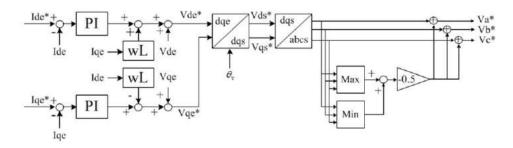

| Figure A.4    | Current Controller for Cascaded H-bridge Converter                          |   |

| Figure A.5    | Block Diagram of Three Module per Phase Cascaded H-bridge Converter . 230   |   |

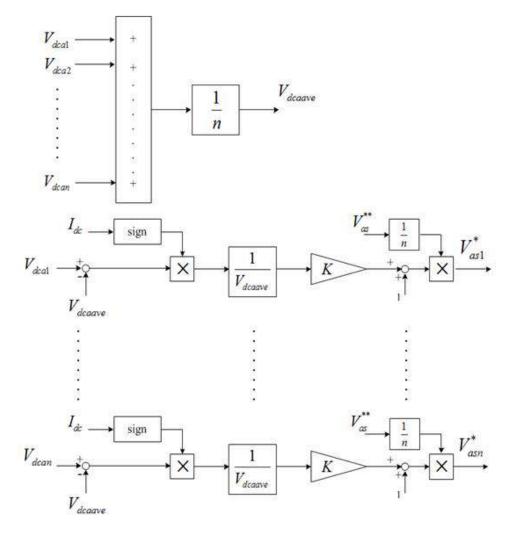

| Figure A.6    | Phase Voltage balancing Controller block diagram                            |   |

| Figure A.7    | Module Voltage Balancing Controller Block Diagram Implemented in Slave      | Ŭ |

| 8             | Controllers                                                                 | 9 |

|               |                                                                             |   |

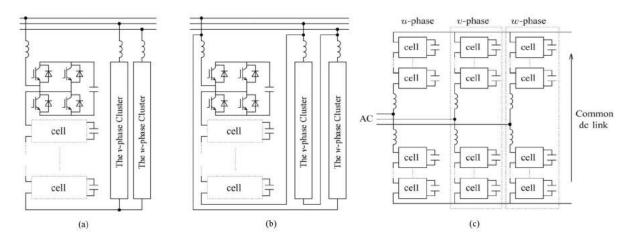

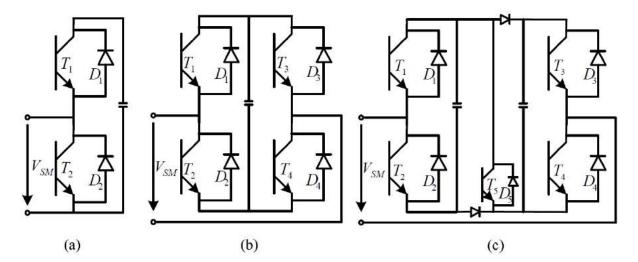

| Figure B.1    | Different Architectures of Modular Multi-level Converters (MMC) a)Single-   |   |

|               | Star Bridge-Cells (SSBC) b)Single-Delta Bridge-Cells (SDBC) c)Double-       |   |

|               | Star Bridge-Cells (DSBC)                                                    | 2 |

| Figure B.2    | Architectures of MMC Sub-modules a)Half-bridge b)Full-bridge c)Double-      |   |

|               | clamped                                                                     |   |

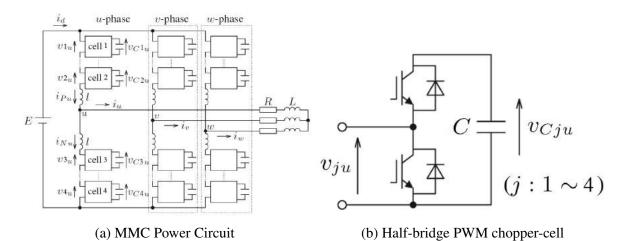

| Figure B.3    | Circuit Configuration of a Double-star MMC                                  |   |

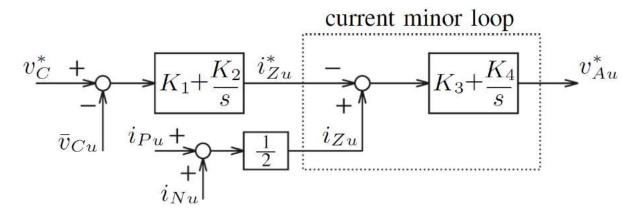

| Figure B.4    | Averaging Control of the Capacitor Voltages                                 |   |

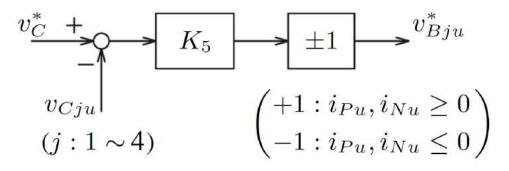

| Figure B.5    | Balancing Control of the Capacitor Voltages                                 |   |

| Figure B.6    | Voltage Command of each MMC Arm                                             | 7 |

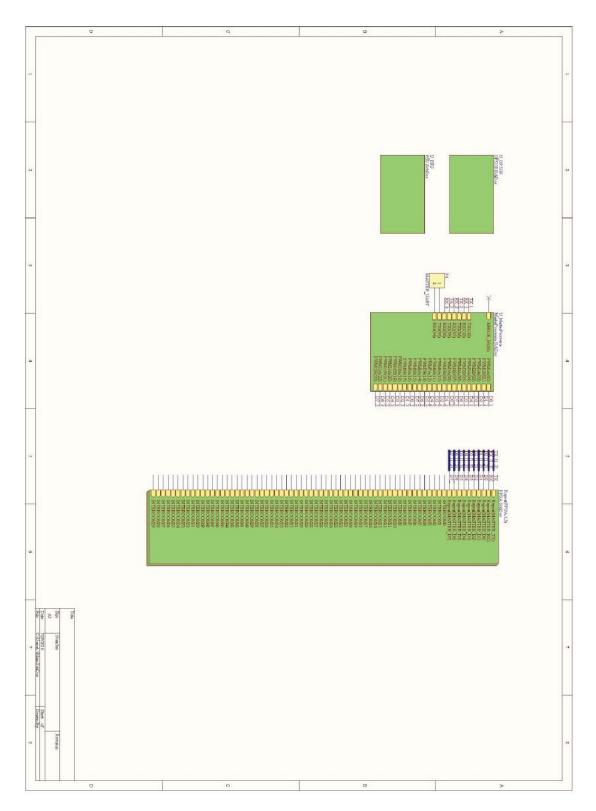

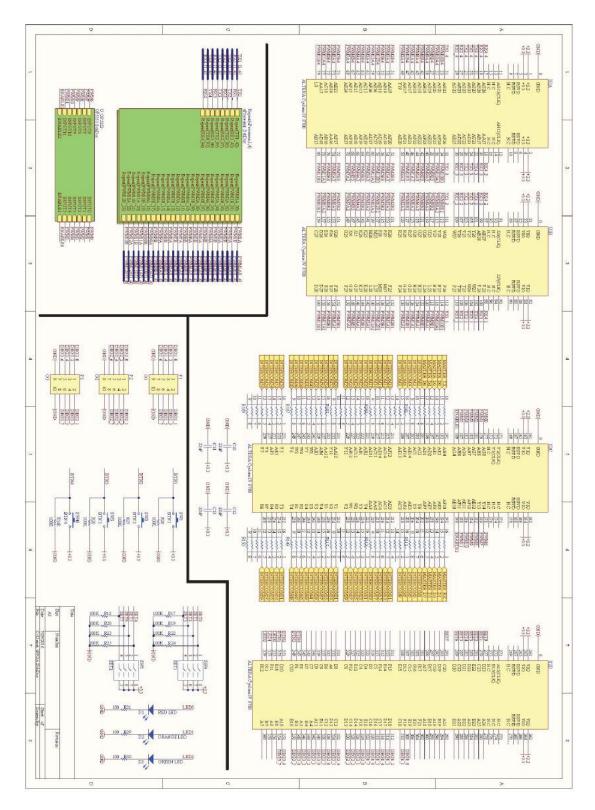

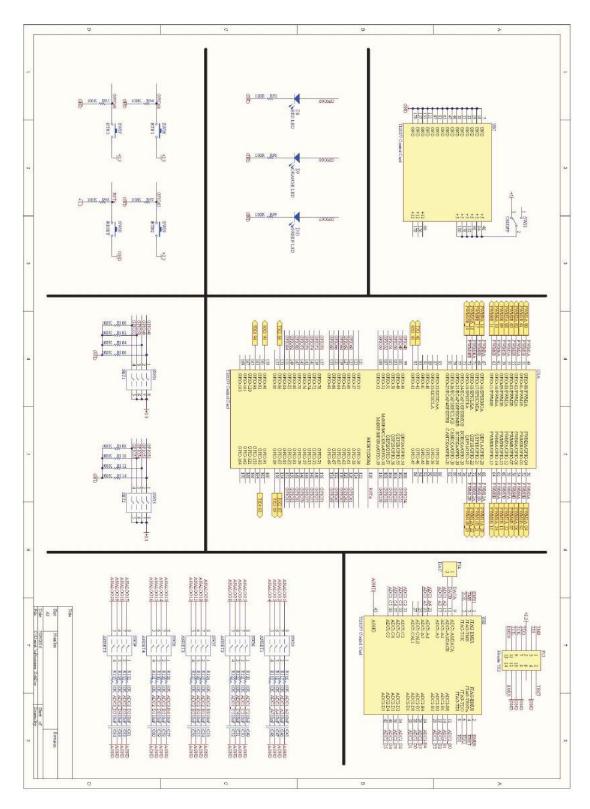

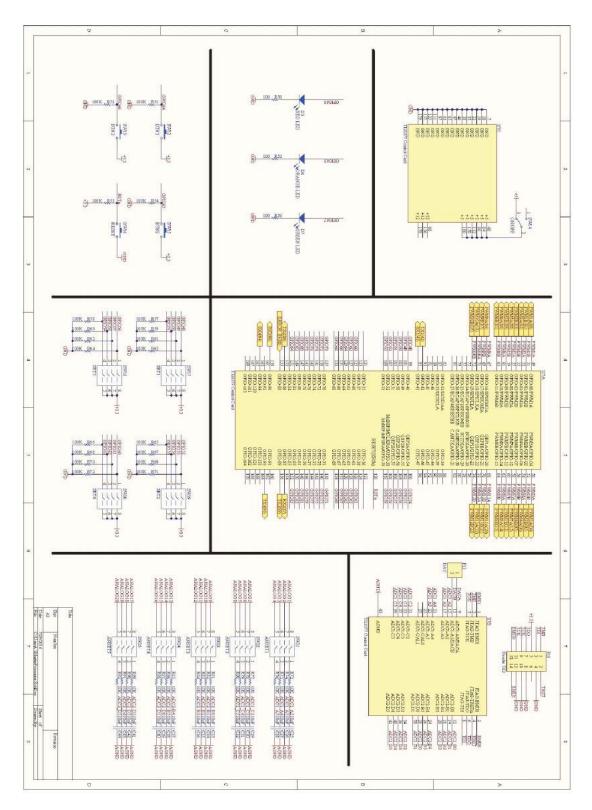

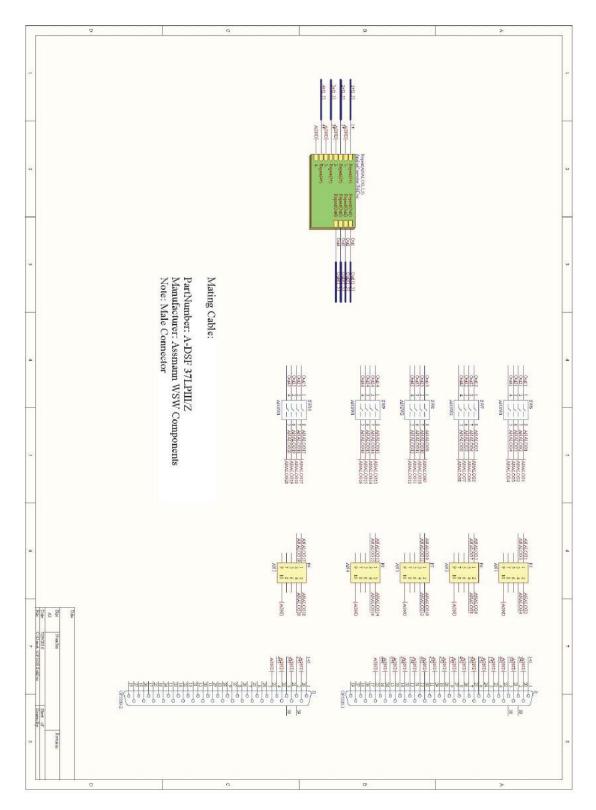

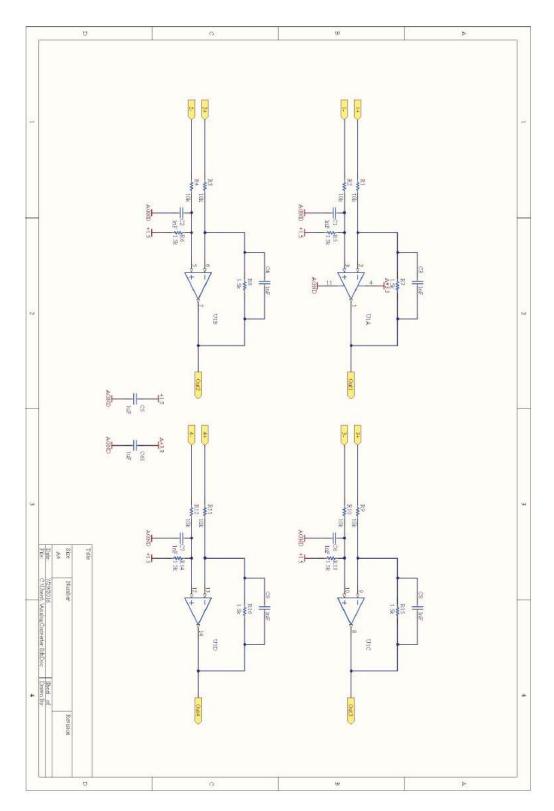

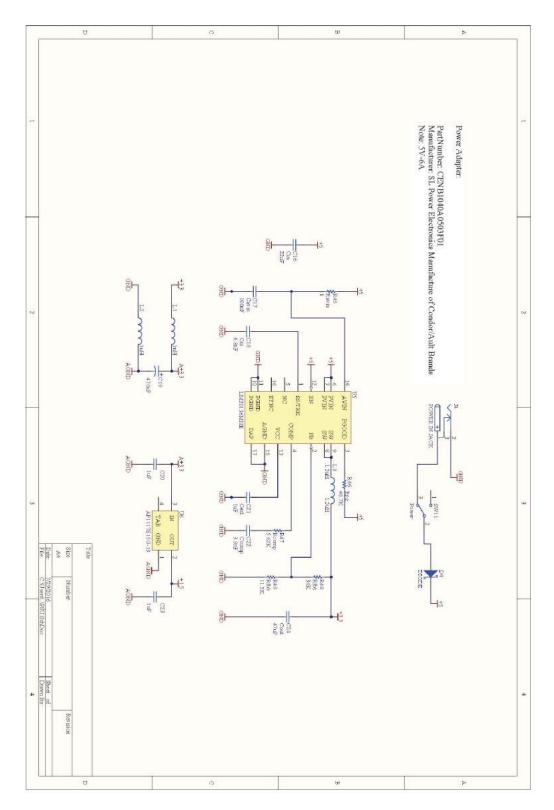

| Figure C.1    | Schematic of the Main Sheet                                                 | 9 |

| Figure C.2 | Schematic of the FPGA Interconnection Configuration Circuit | . 250 |

|------------|-------------------------------------------------------------|-------|

| Figure C.3 | Schematic of Switching Signal Buffers                       | . 251 |

| Figure C.4 | Schematic of Slave Micro Controller                         | . 252 |

| Figure C.5 | Schematic of Master Micro Controller                        | . 253 |

| Figure C.6 | Schematic of Analog Signal Conditioning (Top Level)         | . 254 |

| Figure C.7 | Schematic of Analog Signal Conditioning (Low Level)         | . 255 |

| Figure C.8 | Schematic of Power Supply Unit                              | . 256 |

| Figure C.9 | Printed Circuit Board Design of the Fault-tolerant Test bed | . 257 |

# Chapter 1

# Introduction

### 1.1 Research Background

Facing the challenge of designing fault-tolerant control systems goes back to invention of the microprocessors. Microprocessor functionality is based on physical principles to execute instructions and proceed to the desired result of programmer. The problem with all physical devices is that they are obliged to fatigue and aging during their life time that can cause the device failure. Even if they don't get damaged, they can get affected by transient physical disturbances and give wrong results. All these hard and soft failures in the controller chip can cause the system failure. In some systems, the failure is not tolerated and the harm the failure can cause, motivates the engineers to design a system that can handle the failures. Power electronic systems are a good example for demand of such controllers. All electronic devices need power to function and without it, they are dead. Therefore, failure in power section always leads to a failure in the whole system. In order to design a fault-tolerant controller for power electronic systems, it is good to look in to other controllers that have been designed in the past. Server computers, space shuttle controllers and re-configurable VLSI chips are some of the examples.

#### **1.1.1 Tandem Computer**

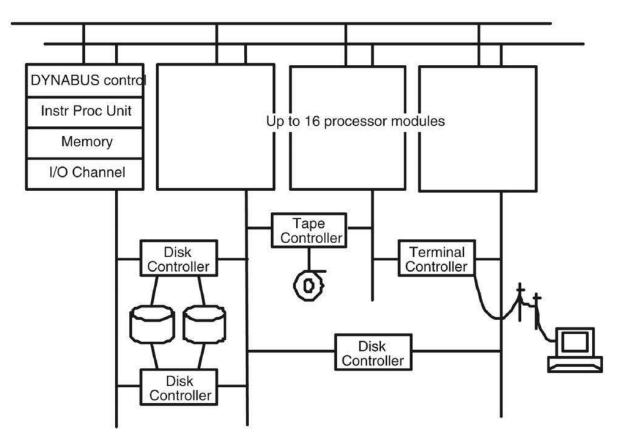

Server computers should process the data correctly and reliably. They should always be available to process the data coming in and going out. In a research done for the risk of data corruption, one error per month was seen in 10000 computers running continuously [40]. Although this is a small error rate, the effect can be huge when it is related to money exchange or stock market. One of the most used computer for non-stop server applications is Tandem computer [48] [10] [11] . The development of this computer has been started in 1974 and is continuing through different brands and corporations. This computer is based on dual or triple module redundancy (DMR or TMR) [12] and the computing power of each module is evolving with time. Figure 1.1 shows the architecture of early Tandem computer that consisted of two to 16 independent processors connected by a pair of interprocessor buses collectively referred to as the Dynabus. Each processor had its own memory and ran its own copy of the operating system. Each processor also had an I/O bus. Each dual-ported I/O controller was connected to two processors'I/O buses, and had internal logic that selected which port was currently the primary path. If a processor or its I/O bus were to fail, the controllers whose primary paths were currently configured to use that I/O bus would switch ownership to their backup paths. Controller configuration was flexible enough that the workload of a failing processor could be spread over multiple surviving processors rather than all being taken over by a single processor. The general design principle was that there be at least two of everything, including power supplies and fans as well as the more obvious processors, controllers, and peripherals. Dual-ported controllers and dual-ported peripherals provided four paths to each device. For disks, the use of host-based RAID-1 mirrored pairs of drives provided eight paths to the data and offered improved data integrity. All of these precaution were done to proof the system from single point of failure (page 4 of [11]).

Figure 1.1: Original Architecture of Tandem Computer (1976)

#### 1.1.2 NASA Shuttle Guidance System

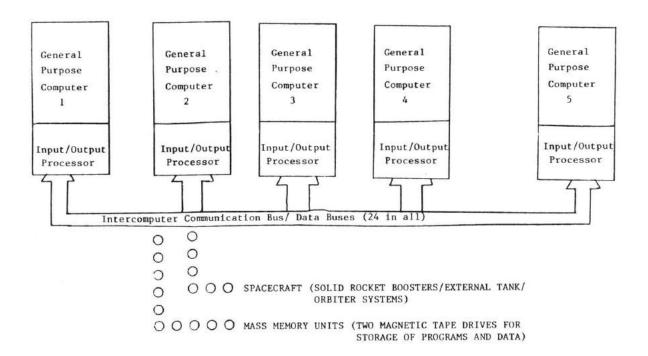

In space shuttles, the degree of robustness is much higher and penta module redundancy is the common controller [88] [71] [80]. Figure 1.2 [99] demonstrate one of the controllers used by NASA during 1970's in different shuttle projects. It consists of five processor unit based on IBM AP-101 which is coupled with I/O processor (IOP) to process the data transfer between different units through data bus. All subsystems on the spacecraft are connected redundantly to at least a pair of data buses. There are 24 of these buses, and the subsystems share them, using multiplexers to control the sharing. Eight of the 24 are "flight-critical data buses" that help fly the vehicle; 5 are used for intercomputer communication among the five general-purpose

computers; 4 connect to the four display units; 2 run to the twin mass memory units; 2 more are "launch data buses," and connect to the Launch Processing System; 2 are used for payloads, and the final pair for instrumentation [71]. All these precautions are necessary to gain high rate of reliability in aerospace projects.

Figure 1.2: Block Diagram of NASA Shuttle Data Processing System

#### **1.1.3** Automotive Control Units

In today's vehicles, as much as 70 micro-controllers may exist for handling the control and safety tasks[56]. Some control tasks like anti-lock braking system (ABS), engine control unit (ECU) and traction control unit (TCU) are directly connected to the safety of the passengers and the design must be fail-safe to decrease the possibility of injuries. Unlike the space and aviation

technology in which designing systems with high availability is desired, in automotive industry the focus is on fail-safe systems. Systems with high availability require much more resources and would increase the cost of the final product. That is not possible in automotive industry with high competition between car manufacturers in decreasing the cost of the vehicle. Instead, the design must be fail-safe and lots of validation tests must be done to make sure there is no bug in design and fabrication stages. In the firmware design, specific standards like MISRA-C have been defined to address the problems in computer programming[20]. These standards help reducing the common error that programmers make in development stages.

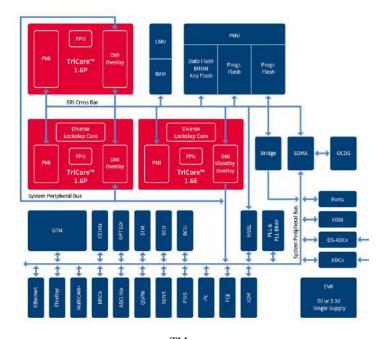

The new microprocessors for the automotive industry are much sophisticated than before. Figure 1.3 shows the architecture of a tri-core processor on a single chip. Using multiple core to perform a task will enables the firmware development group to design a fault-tolerant controller architecture. Since all the hardware is integrated, the overall cost won't change very much.

Figure 1.3: Architecture of Tricore<sup>TM</sup> ver-1.6 Automotive Micro-controller[2]

#### 1.1.4 Fault-tolerant WSI/VLSI Architecture

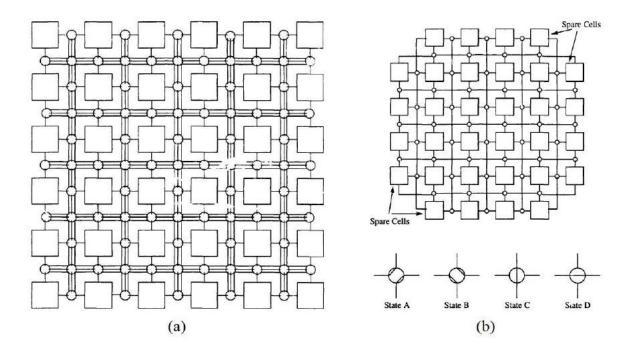

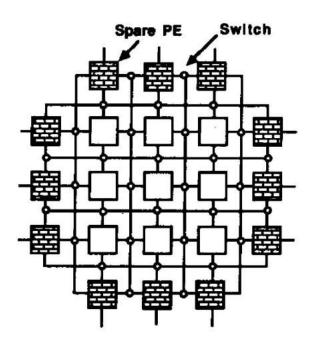

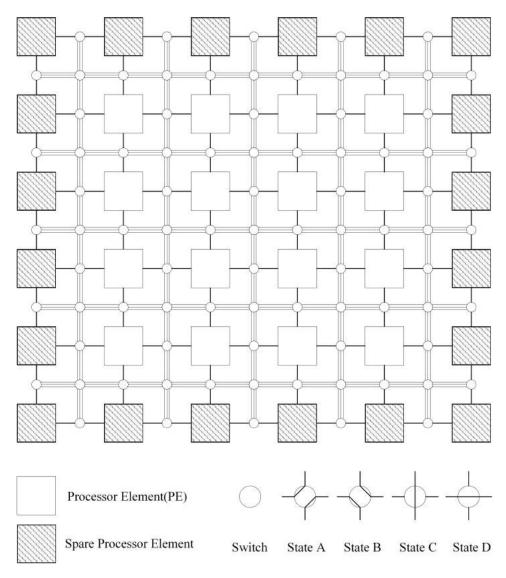

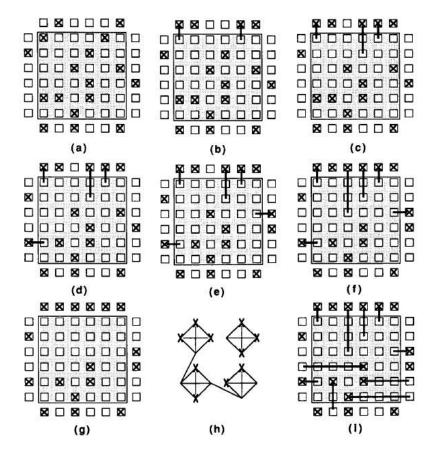

In most of the digital signal processing (DSP) applications, a huge amount of data is processed to get the final result. One of the good examples of fault tolerancy in DSP systems is the re-configurable processor array that has been designed by a team of researchers in Stanford university [98]. As it is shown in Figure 1.4, an array of processing elements (PE) have been connected to each other through a set of configurable data bus. Many computations in matrix algebra can be conveniently carried out on an array of identical processing elements. VLSI technology provides an inexpensive approach to building such arrays. However, during the fabrication process or during operation, some of the processing elements in a large array are inevitably going to be faulty. Spare PEs and extra routing hardware are often provided so that a fault-free array can be constructed; such reconfiguration capability can be used to increase the yield, and to guarantee fault tolerance in applications where failure is not permissible.

Figure 1.4: Re-configurable Processor Array (a)Before Configuration (b)After Configuration

There are difficulty in hardware and software design of the system. A systematic design procedures for a class of structured algorithms that often encountered in signal processing applications has been developed by that team which is called regular iterative algorithm (RIA). Once a Regular Iterative Algorithm is designed for a given problem, then one can use the systematic design theory to generate efficient processor arrays. The general models that has been explored consist of a set of identical processors embedded in a flexible interconnection structure that is configured in the form of a rectangular grid. This grid can be configured to implement the desired DSP algorithms. In each column of the grid, one extra PE is available to form a N(N+1) matrix of PE(1.5). In the case of failure, the faulty module will be bypassed and the restructured array processor is able to perform the same function like the time before failure.

Figure 1.5: Architecture of Array Processor with Spare Processing Element at the Edges

The similarity between array processors and modular multi-level converter is that several modules are available and the architecture of these modules is changeable. In the following chapters, the architecture of fault-tolerant array processor will be investigated in detail and will be modified to match the criteria of controller for modular multi-level converter.

## **1.2** Motivation

Distributed controllers are much complicated than centralized controllers, hence, there should be justification for using such controllers in the system. In multi-level converters, the are several power modules connected to each other to convert energy from one form to another form. This type of converter is distributed and using distributed controllers doesn't make big change in the system. In the following sections different architectures of multi-level converters will be reviewed and best converter for distributed controller will be selected. After that, application and benefits of such converter systems using fault-tolerant controller will be evaluated.

# **1.2.1** Comparison of Multi-level Converters and Feasibility of Using Distributed Fault-tolerant Controller

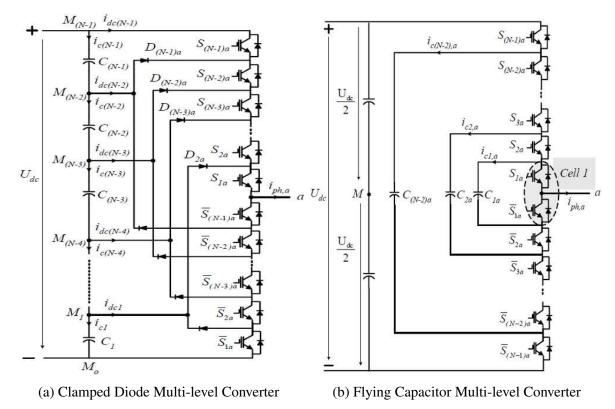

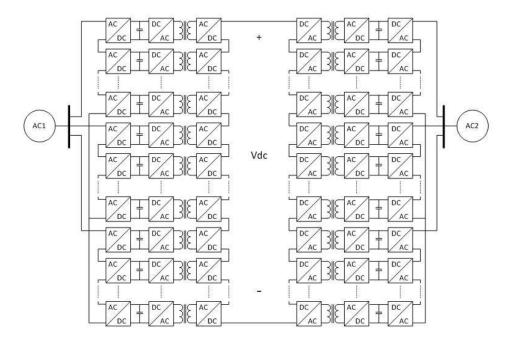

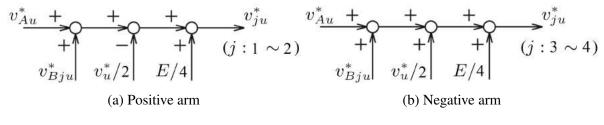

Multi-level converter is a power electronics converter that synthesizes the modulating waveform (usually a sinusoid) using multiple voltage levels. These voltage levels are created using capacitor voltage division network. Figure **??** and **??** shows four different multi-level converters. By turning on the IGBTs, it is possible to connect to capacitors and change the output voltage[89, 26].

In clamped diode multi-level converter (figure 1.6a), it is necessary to turn on the IGBTs that are in the conduction path to the phase output in order get the voltage level of that capacitor. Therefore the sink and sourcing current don't pass a symmetrical line. In flying capacitor multi-level converter, the output voltage is synthesized by arranging the connection style of the floating capacitors. The number of capacitor in series and the polarity of them defines the output voltage. These two type of multi-level converters are **not** modular and there are not the best options for implementing the fault-tolerant controllers.

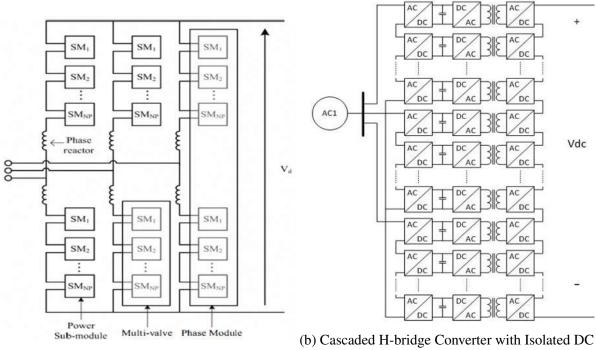

Figure ?? demonstrate another category of multi-level converters in which the power modules

Figure 1.6: Diagram of Two Non-modular Multi-level Converters

can be scaled up easily by adding them in series. Modular multi-level converter (MMC) as well as Cascaded H-bridge converter synthesize the output voltage by changing the capacitors arrangement from DC grid to the output phase (details in Appendix A and B). Each sub-module is separable as a whole block, therefore if one module fails, it is possible to bypass the failed module and converter can continue its operation. By taking advantage of this capability and using distributed controllers, it is possible to form fault-tolerant controller as well as fault-tolerant converter.

# **1.2.2** Performance and Reliability Enhancement in Power Delivery using Modular Multi-level Converter with Distributed Fault-tolerant Controller

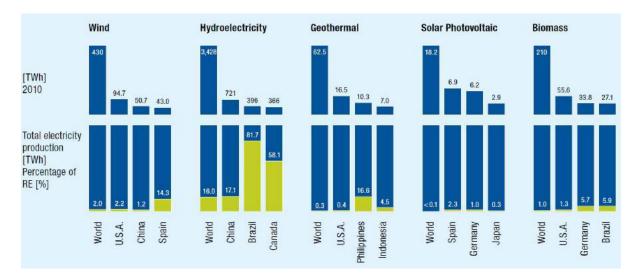

Along with the big changes in power generation, transmission and distribution, the need for intelligent controllers has increased. The new systems need high speed signal processors to handle the tasks. Renewable energy is one of the areas that require intelligent converters. Figure 1.7 shows the renewable energy usage of each country in 2010 [54] [5].

Energy conversion in renewable sources is not as same as the traditional fossil sources. In most

Figure 1.7: Renewable Energy Usage by Each Country

cases, the energy harvested from renewable sources can't be used directly by customers and need conversion by power electronic systems. The voltage and current rating of the generated energy is high and simple converters can't be implemented for this application. Modular multi-level converter (MMC) is one of the converters that can handle this power rating (Figure 1.8a). The

problem with this converter is its complexity in control and drive. Tens or hundreds of modules are connected together and each one should be triggered separately.

(a) Double-Stat-Configured MMC Converter

(b) Cascaded H-bridge Converter with Isolated DC Capacitor

Figure 1.8: Diagram of Modular Multi-level Converters [54]

One of the biggest advantage of this converter is that the total rating of all the modules are higher than the generated power and it is possible to take out some of the modules without interrupting its functionality [25]. To achieve this benefit, controllers must have this capability too. If controllers are distributed just like the power modules, then it is possible to have fault tolerant controllers for the converter.

The dissertation is trying to implement distributed control of the MMC and convert the designed system with fault-tolerant controllers. If failure happens in one of the modules (either in the

controller or the power electronic circuit), it would be detected and isolated from the system. This will increase the availability and reliability of the converter by a large factor because the faulty module can be replaced meanwhile the converter system is operating. From the economical point of view, repairing modular multi-level converters might take a lot of time and in conventional controlled system, power converters should be turned off for the repair period. Down time will increase the cost of repair and it is not desirable. These improvements as well as the economical benefits are the main motivation for the proposed architecture in the dissertation.

## **1.3 Research Contributions**

This dissertation contains many contributions to fault-tolerant controller design for multi-level converter. Some of these contributions are listed as follows:

- Defining different architectures for distributed control of multi-level converters

- Proposing synchronization methods for distributed controllers in multi-level converters

- Applying the control method to cascaded H-bridge converter (CHB) and modular multilevel converter (MMC)

- Reviewing literature related to fault origins in hardware controllers and available solutions in controller architectures and apply it to the proposed controller

- Proposing a new controller architecture for multi-level converters with fault-toleration capability

- Proposing second generation of fault-tolerant controller for modular multi-level converters and focus on synchronization methods related to this type of controller.

- Categorizing fault-detection methods and implementing them for hardware controller and power devices

- Simulating the proposed controller for cascaded H-bridge multi-level converter

- Estimating the lifetime for the controller card and components that have been used inside the controller card

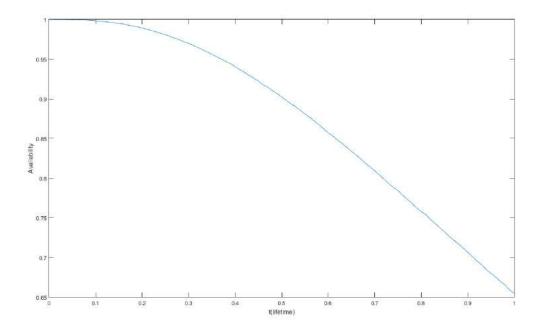

- Modeling the controller architecture using Markov chain, estimating the availability of the proposed controller and assessing the reliability of the proposed controller

- Researching fault-tolerant firmware design methods and techniques to limit failure in software and techniques to bypass those failures

- Implementing proposed controller architecture in hardware in the loop (HIL) simulation for CHB and MMC converter and designing a real CHB converter to test the proposed controller

# Chapter 2

# Synchronization and Architectures of Distributed Controllers for Modular Multi-level Converters

## 2.1 Introduction

Due to limited breakdown voltage and nominal current of controlled switches (SCRs or IGBTs), several devices must be connected in series and parallel to tolerate the required line voltage and current. In some applications, designers are forced to utilize several converter modules working together to deliver the electrical power. As a result, several controllers might be required to generate the switching signals of the controlled switches. These controllers must be synchronized with each other in order to work properly. To achieve this goal, proper control architecture is required to synchronize all the controllers and determine how each controller communicates with other controllers. In this chapter, different control architectures including series (daisy chain), parallel and parallel-daisy are explored and compared. There are different problems

associated with designing such converters including synchronizing the distributed controllers to the observatory controller and timing consideration in communication. The focus of this chapter would be on architectures that fit for the design of a fault-tolerant controller.

## 2.2 Architectures of Distributed Controllers

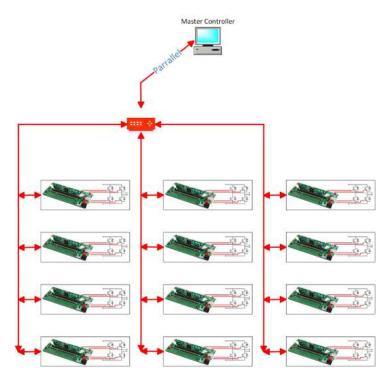

There are different ways to connect distributed controllers together and to the master controller. Architectures of distributed controllers for modular multi-level converters can be categorized in three sections.

In **daisy chain** architecture, each controller is connected directly to the adjacent controller (Figure 2.1). The nearby controllers can communicate fast, but since the entire process is being controlled by a supervisory controller (master controller), this benefit cannot be utilized in the system. A data packet from master should pass through all modules to reach the last controller. This can cause data latency and can lead to instability in some cases. To overcome this issue, the data packet must be transferred faster compared to control time step (using fiber optic) and be sent bit by bit without being buffered in each module. The latency in data arrival is more critical when pulse width modulation (PWM) signal synchronization is required to be done. Due to harmonics considerations, each PWM signal in any controller should be synchronized to a reference time stamp and the resolution of time difference should be in the order of tens of nano seconds.

Beside all these cons, the major benefit of this architecture is its ability to be implemented by fiber optic based decoupled hardware. Since data line is point to point, fiber optic communication is possible and this will give a high degree of robustness to the entire design. The other benefit is that adjacent controllers can share data with each other to assure correct functionality. This would be helpful in the design of fault-tolerant controller.

Figure 2.1: Daisy-Chain Distributed Controller Architecture

In **parallel architecture** (Figure 2.2), all controllers share a common communication link and they are able to send and receive data through the same link. However, the permission is being controlled by the master controller and slave controllers are not able to communicate directly with each other. When a data packet is sent, it will propagate to all controllers at the same time and they can read the packet. This will make the synchronization process much easier but bandwidth would be limited due to the fact that all controllers share the same data link. This architecture can easily be implemented using differential pair signals. Good example of this type of communication is RS-485 standard. This standard enables us to have up to 256 devices in the system with baud rate up to 10 Mbps. The communication is half duplex i.e. only one device can transmit data at any time. The pay off in this architecture is the ability of master controller to send data packets to all of the controllers simultaneously. Electrical precautions must be considered in the design and twisted wire pair should be used in transmission to avoid interference and noise issues.

Figure 2.2: Parallel Distributed Controller Architecture

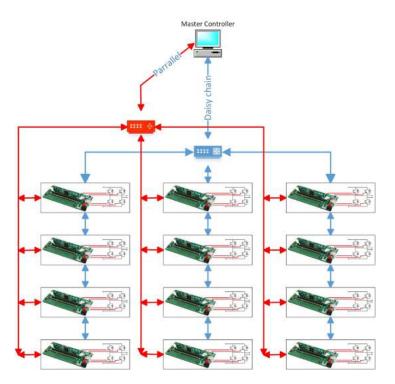

To overcome limitations of two architectures, we can combine both of the typologies together in the modular multi-level converter. In **parallel-daisy** architecture (Figure 2.3), adjacent module can communicate with each other just like the daisy chain architecture. This communication like is used to check the status each controller and in the case of failure in the controller, its function can be done by the neighbor controller. There is also a parallel communication link that connects all slave controllers to the master controller and it would be

used to synchronize the controllers (like parallel architecture). This architecture would be used in other chapter as the base for designing fault-tolerant distributed controller.

Figure 2.3: Parallel-Daisy Distributed Controller Architecture

The comparison between all architectures can be summarized in table 2.1.

| Architecture   | Network Realization                                                        | Advantages                                                        | Disadvantages                                                                                                      |

|----------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Daisy Chain    | Any type of serial<br>communication<br>including UART,<br>SPI, Fiber Optic | Short signal path,<br>Scalability, Fiber op-<br>tic compatibility | Data latency (from master<br>to slave), Vulnerable data<br>link (one connection short-<br>age can stop the system) |

| Parallel       | One to many pro-<br>tocols (RS-422/485,<br>CAN, I2C)                       | Scalability, Broad-<br>casting ability                            | Vulnerable data link (short<br>circuit in data link can stop<br>system functionality)                              |

| Parallel-Daisy | Combination of se-<br>rial protocols                                       | Scalability, Broad-<br>casting ability, Fault<br>tolerancy        | Complex Packet process-<br>ing                                                                                     |

Table 2.1:

Comparison between Architectures of Different Distributed Controller Systems

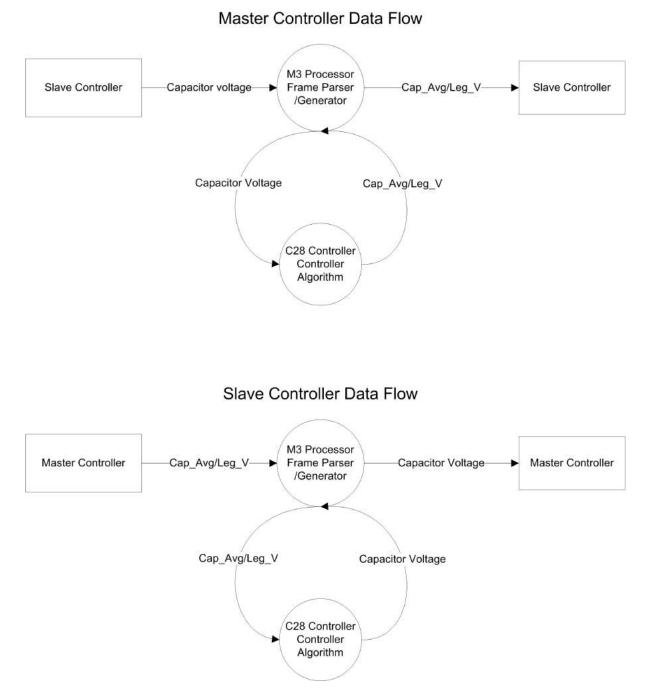

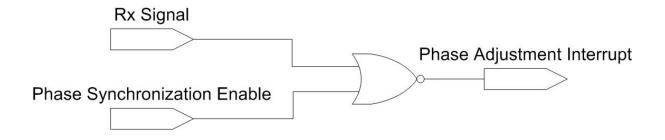

# 2.3 Synchronization of Distributed Controllers in Packet Switched Networks

In distributed systems, slave controllers must be synchronized with the master controller [59]. The synchronization process helps the controllers to accomplish tasks in a timely manner and follow the schedule. Frequency (rate of oscillation), phase (start of the oscillation) and time (number of oscillations) are three important parameters that must be passed during synchronization from the master to the slaves. All of these variables are function of the oscillator frequency and any frequency difference may cause error in the system. These error can be formulated as given below:

$$f_e = f_m - f_s \Rightarrow \omega_e = 2\pi f_e$$

$$t_e = \frac{f_e}{f_m} \times t$$

$$\varphi_e = \omega_e \times t + \theta_{e_0}$$

(2.1)

In the above equations, the frequency of the master controller oscillator  $(f_m)$  is assumed as the reference frequency and its difference with the slave controller oscillator frequency  $(f_s)$  is the error  $(f_e)$ . The time error  $(t_e)$  and phase error  $(\varphi_e)$  are function of the oscillator frequency as well.