#### ABSTRACT

RENGARAJAN, SATISH. Characterization and Analysis of 10 kV Generation-3 Silicon Carbide Power MOSFET Model. (Under the direction of Dr. Subhashish Bhattacharya.)

The semiconductor industry is primarily dominated by devices made out of Silicon (Si). However, great deal of research and recent developments in the technology of Silicon Carbide (SiC) have opened multiple doors for their use in various applications which were earlier utilizing Silicon. A quick comparison between Si and SiC would reveal superior characteristics of the SiC counterparts like higher critical electric field, thermal conductivity, operating temperature, current density etc [2]. Observing these trends, it is possible to predict that the future of the semiconductor industry would see a tremendous increase in SiC devices and progressive replacement of the existing technology as the cost drops over the years. This calls for proper modelling and analysis of SiC power devices to accurately predict their performance in power electronic converters. In this thesis, a detailed study of the 10 kV 18 A Generation-3 SiC model is performed in SABER software and compared to an existing model in the market. The module (maximum current capacity of 240 A) is manufactured by WOLFSPEED and is the latest addition to the previous generation of MOSFETs. SABER is a platform for modelling and simulating physical systems which enables full system prototyping for applications in analog/power electronics, electric power generation and mechatronics. SABER simulations are carried out to obtain results that characterize and predict the behaviour of the 10 kV device. This includes obtaining the static, dynamic, gate charge and body diode characteristics of a single MOSFET die model. In addition, the actual die of the Gen-3 MOSFET is characterized with the Power Device Analyzer/Curve Tracer B1505 of Keysight Technologies. The results obtained from the Saber model are compared with the ones from the curve tracer. The accuracy of the model can be ascertained in this process and corrections can be made to obtain a better Saber model in the future. The work presented here would include complete characterization and modeling of parasitics, development of device models, comparison of these device models and analysis of power electronic converters with these devices. Once complete characterization data of the model is obtained through SABER, the focus would be in calculating losses, transient times and modelling series connection in high voltage circuits. As the input voltage in the converter is increased close to or beyond the ratings of the module, multiple series connected models are used in such applications. Voltage sharing between the devices becomes a matter of concern due to slight differences in device parameters. The thesis also sheds some light on this issue and details the design of a balancing snubber circuit to minimize the voltage mismatch. The final chapter provides a comparative study of the switching losses in the half bridge configuration through hardware testing and Saber simulations for different values of DC input voltage and switching currents. The differences caused by parasitic ringing during the transitions can be understood in further detail.

© Copyright 2018 by Satish Rengarajan

All Rights Reserved

### Characterization and Analysis of 10 kV Generation-3 Silicon Carbide Power MOSFET Model

by Satish Rengarajan

#### A thesis submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Master of Science

**Electrical Engineering**

Raleigh, North Carolina

2018

APPROVED BY:

Dr. Jayant Baliga

Dr. Douglas Hopkins

Dr. Subhashish Bhattacharya Chair of Advisory Committee

#### DEDICATION

We are all driven forward in our journey to happiness and success by the people who really care about us. Over the course of this journey, my family has been a pillar of great support helping me carry on past the temporary hurdles and challenges that I faced while working on this project. I was also lucky to be surrounded by bright minds over the past two years of my graduate studies at NC State University. I would like to dedicate this work to my family and those dear friends who supported me throughout the thesis work.

#### Amma, Appa this is for you!

#### BIOGRAPHY

Satish Rengarajan was born in the town of Madurai in Tamil Nadu located in South India. He grew up in Mysore and Chennai and completed his Bachelor's degree in Electrical and Electronics Engineering from National Institute of Technology, Tiruchirappalli (NIT- Trichy). After his graduation, he worked with Larsen and Toubro Power Transmission and Distribution in Doha, Qatar and was involved in substation projects of KAHRAMAA and Qatar Petroleum. Later, he joined SunEdison Energy India Pvt Limited in Chennai and started his work in the company's design engineering department. In 2016, he joined North Carolina State University to pursue his Master's in Electrical Engineering and specialized in Power Electronics. He has worked at the Future Renewable Electric Energy Delivery and Management (FREEDM) Systems Center as a graduate researcher. In 2017, he completed his internship at Johnson Controls Inc. located in New Freedom, PA in its Power Electronics and Motor Drives department.

#### ACKNOWLEDGEMENTS

Firstly, I would like to thank my research advisor Dr. Subhashish Bhattacharya for guiding me over the course of my thesis and for the help he provided for the fulfillment of credits for my Master's degree. I would like thank Ashish Kumar and Anup Anurag for their constant support and valuable suggestions when I was getting the test results. They were very helpful throughout my research contributing towards circuit design and converter modeling. I would like to thank Utkarsh, Dipen, Sayan, Sanket, Anuj and Kijeong for their valuable inputs and suggestions during the course of completing my thesis. I also would like to thank Dr. Baliga and Dr. Hopkins for graciously accepting to be a part of the committee for the defense. Finally, I would like to thank the lab manger, Mr. Hulgize for his support in maintaining the research space required for this thesis.

| LIST OF TABLES                    |                                                          |           |  |  |

|-----------------------------------|----------------------------------------------------------|-----------|--|--|

| LIST OF                           | FIGURES                                                  | vii       |  |  |

| Chapter                           | 1 INTRODUCTION                                           | 1         |  |  |

| 1.1                               | Motivation                                               | 3         |  |  |

| 1.2                               | Assumptions and introduction to SABER:                   | 4         |  |  |

| 1.3                               | Organization of Thesis                                   | 6         |  |  |

| Chapter                           | 2 Characterization of 10 kV die model                    | 8         |  |  |

| 2.1                               | Output Characteristics                                   | 8         |  |  |

| 2.2                               | Transfer Characteristics                                 | 13        |  |  |

| 2.3                               | Gate Charge Characteristics                              | 17        |  |  |

|                                   | 2.3.1 Miller Effect and estimation of gate charging time | 22        |  |  |

| 2.4                               | Parasitic Capacitances                                   |           |  |  |

|                                   | 2.4.1 $C_{iss}$ Calculation                              |           |  |  |

|                                   | 2.4.2 $C_{oss}$ Calculation                              |           |  |  |

|                                   | 2.4.3 $C_{rss}$ Calculation                              |           |  |  |

| 2.5                               | Leakage Current.                                         |           |  |  |

| 2.6                               | Body Diode Characteristics                               |           |  |  |

|                                   | 2.6.1 Charge analysis of the Saber body diode model      |           |  |  |

| Chapter                           | 3 Switching losses and transition times                  | 45        |  |  |

| 3.1                               | Case <i>I</i>                                            | 46        |  |  |

| 3.2                               | Case <i>II</i>                                           | 48        |  |  |

| 3.3                               | Case III                                                 | 51        |  |  |

| Chapter                           | 4 Series connection and snubber design                   | 57        |  |  |

|                                   | 4.0.1 Double Pulse Test                                  | 58        |  |  |

| Chapter 5 Saber Power MOSFET tool |                                                          | 67        |  |  |

|                                   | 5.0.1 Power Converter Simulation:                        | 71        |  |  |

| Chapter                           | 6 Hardware validation (10 kV Gen-3 SiC MOSFET)           | 73        |  |  |

| Chapter                           | 7 Conclusion and future work                             | <b>BO</b> |  |  |

| APPEND                            | DICES                                                    | 85        |  |  |

# **TABLE OF CONTENTS**

### LIST OF TABLES

| Table 2.1 | $R_{DS,ON}$ vs temperature (calculated at $V_{GS}$ = 15 V and $I_D$ = 2 A)- Saber model                                 | 12 |

|-----------|-------------------------------------------------------------------------------------------------------------------------|----|

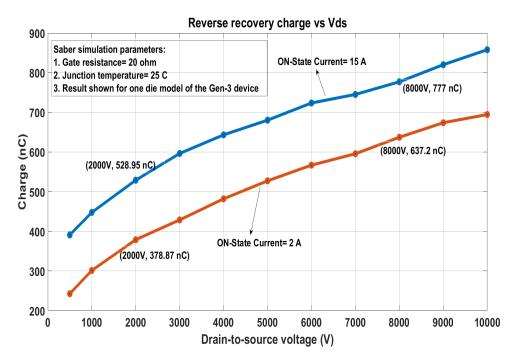

| Table 2.2 | Gen-3 internal body diode switching characteristics: Saber simulation                                                   | 42 |

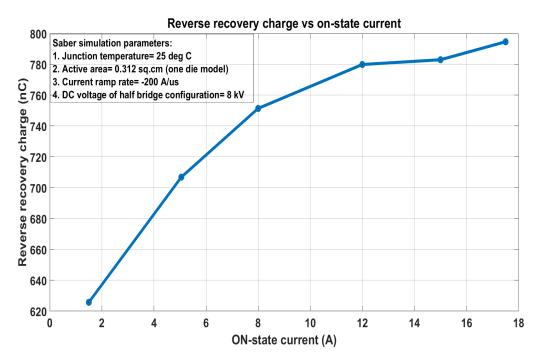

| Table 2.3 | $Q_{rr}$ as a function of ON-state current when di/dt= -200 A/us: Saber simulation                                      | 43 |

| Table 2.4 | $Q_{rr}$ at $V_{DC}$ = 8 kV and diode current = 15 A: Saber simulation                                                  | 43 |

|           |                                                                                                                         |    |

| Table 4.1 | Voltage mismatch with $R_d = 5 \Omega$ , $R_s = 1 M\Omega$ , $C_d = 1 nF$ , $R_G = 20 \Omega$ (Saber results)           | 61 |

| Table 4.2 | Voltage mismatch with $R_d = 1 \Omega$ , $R_s = 1 M\Omega$ , $C_d = 1 nF$ , $R_G = 20 \Omega$ (Saber results)           | 63 |

| Table 4.3 | Voltage mismatch with $R_d = 1 \Omega$ , $R_s = 1 M\Omega$ , $C_d = 0.5 \text{ nF}$ , $R_G = 20 \Omega$ (Saber results) | 63 |

| Table 4.4 | Snubber circuit losses (Saber results)                                                                                  | 64 |

|           |                                                                                                                         |    |

#### **LIST OF FIGURES**

| Figure 1.1               | Basic Power MOSFET Structure                                                                                   | 1  |

|--------------------------|----------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1<br>Figure 2.2 | Saber simulation to obtain output characteristics                                                              | 9  |

|                          | curve tracer)                                                                                                  | 10 |

| Figure 2.3               | Output Characteristics when junction temperature= $175$ °C (Saber model)                                       | 11 |

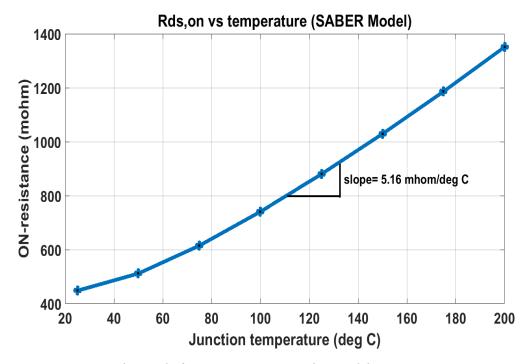

| Figure 2.4               | ON- resistance $(R_{DS,ON})$ of Gen-3 SiC MOSFET Saber model vs temperature .                                  | 12 |

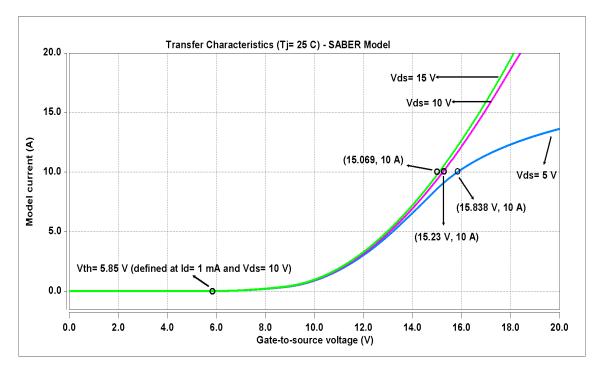

| Figure 2.5               | Transfer Characteristics when $T_i = 25 ^{\circ}\text{C}$ - from Saber model                                   | 14 |

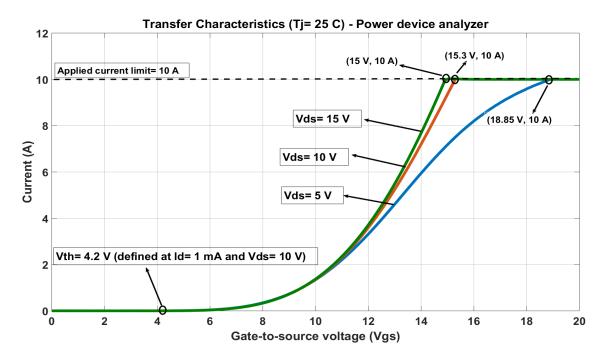

| Figure 2.6               | Transfer Characteristics when $T_i = 25^{\circ}$ C- From power device analyzer/curve                           |    |

|                          | tracer                                                                                                         | 14 |

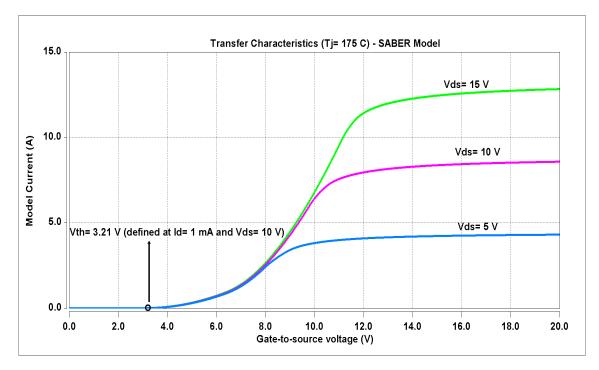

| Figure 2.7               | Transfer Characteristics when $T_i = 175 ^{\circ}$ C (Saber model)                                             | 16 |

| Figure 2.8               | Variation of Threshold voltage $(V_{th})$ with respect to temperature                                          |    |

| Figure 2.9               | Simulation Schematic to obtain gate charge characteristics                                                     |    |

| Figure 2.10              | Gen-3 Saber device model: gate charge characteristics                                                          |    |

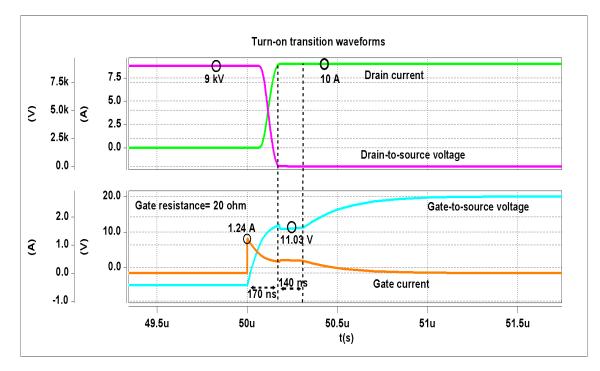

| Figure 2.11              | $V_{DS}$ , $I_D$ , $V_{GS}$ and $I_G$ when $V_{in} = 1$ kV, current = 10 A and $R_G = 20 \Omega$ (Saber model) |    |

| Figure 2.12              | $V_{DS}$ , $I_D$ , $V_{GS}$ and $I_G$ when $V_{in} = 9$ kV, current = 10 A and $R_G = 20 \Omega$ (Saber model) |    |

| Figure 2.13              | Schematic- equivalent capacitance                                                                              |    |

| Figure 2.14              | Equivalent circuit representation during turn-on                                                               |    |

| Figure 2.15              | Calculation of parasitic capacitances of the Saber model                                                       |    |

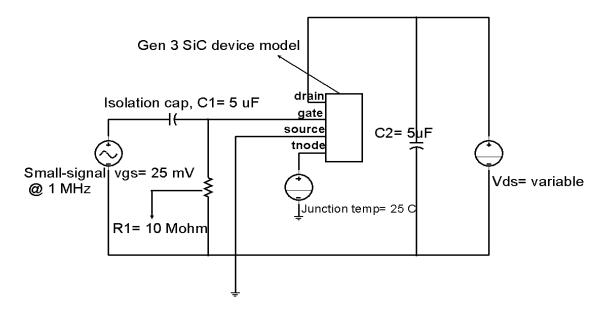

| Figure 2.16              | Saber simulation to obtain $C_{iss}$                                                                           | 26 |

| Figure 2.17              | Small-signal voltages and currents- $C_{iss}$ calculation of Saber model                                       |    |

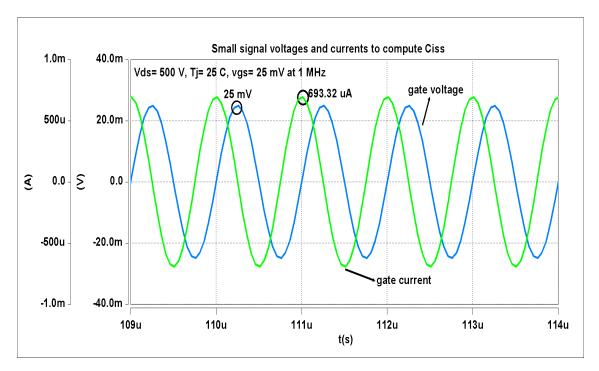

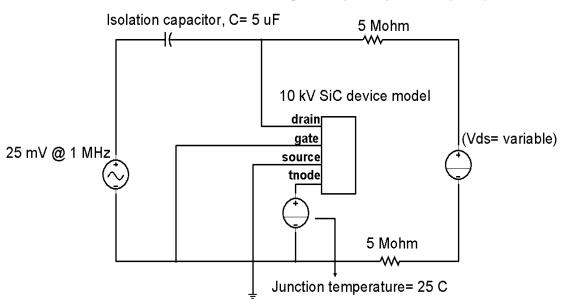

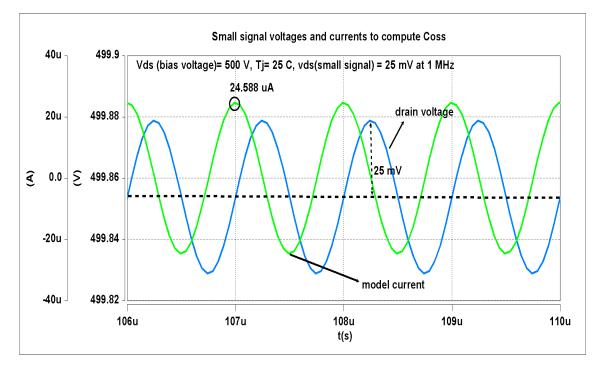

| Figure 2.18              | Saber simulation to obtain $C_{oss}$                                                                           |    |

| Figure 2.19              | Small signal voltages and currents- $C_{oss}$ calculation of Saber model                                       |    |

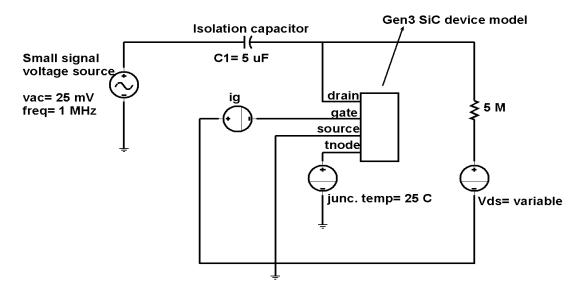

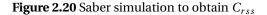

| Figure 2.20              | Saber simulation to obtain $C_{rss}$                                                                           | 29 |

| Figure 2.21              | Small signal voltages and currents- $C_{rss}$ calculation of Saber model                                       | 30 |

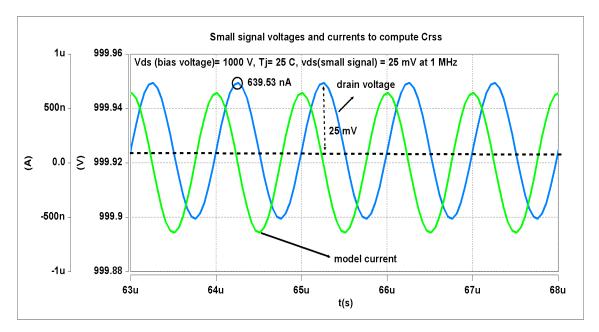

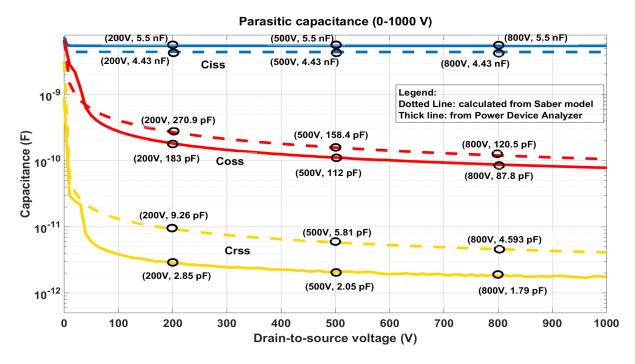

| Figure 2.22              | Parasitic capacitance of Saber model vs $V_{DS}$                                                               | 31 |

| Figure 2.23              | Parasitic capacitance vs $V_{DS}$ (zoomed-in plot) (Saber vs Curve Tracer values).                             | 31 |

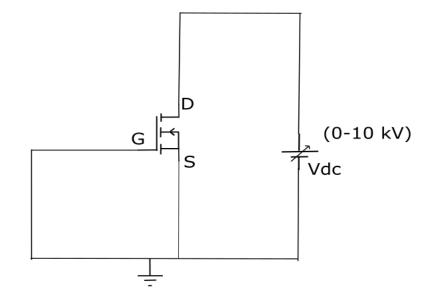

| Figure 2.24              | Schematic- leakage current                                                                                     | 32 |

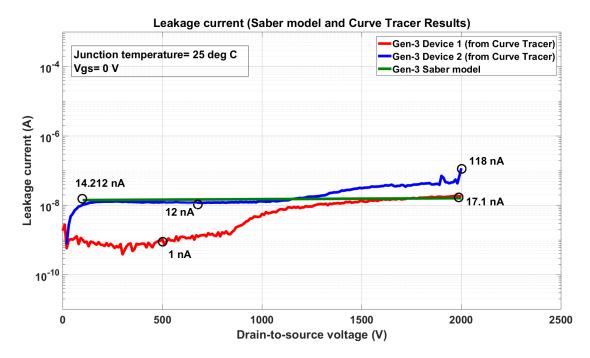

| Figure 2.25              | Schematic- leakage current: Saber model and actual device                                                      | 33 |

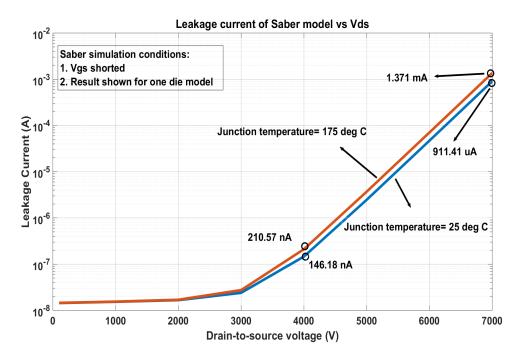

| Figure 2.26              | Leakage current vs $V_{DS}$ (Saber model)                                                                      | 34 |

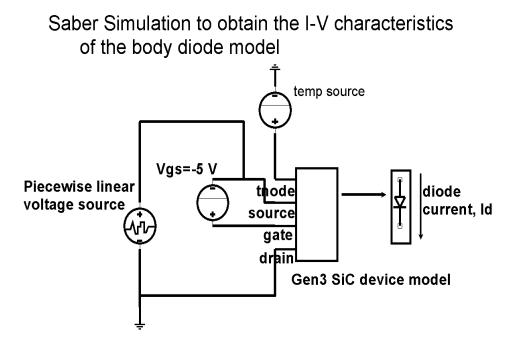

| Figure 2.27              | Schematic body diode forward characteristics                                                                   | 35 |

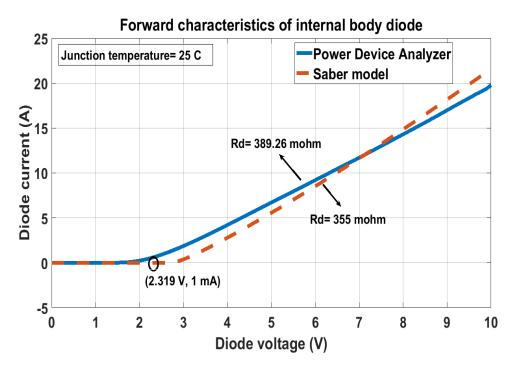

| Figure 2.28              | I-V Characteristics of the Gen-3 internal body diode                                                           | 36 |

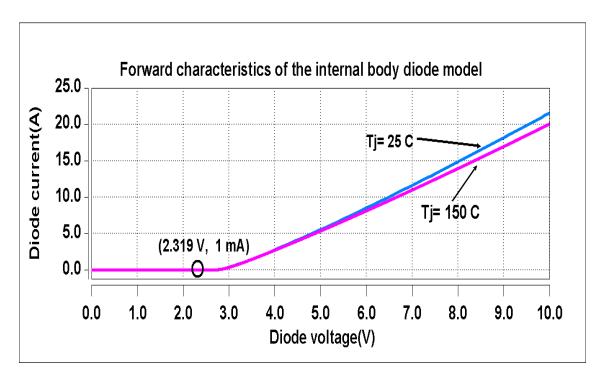

| Figure 2.29              | I-V Characteristics (Saber model): body diode                                                                  | 37 |

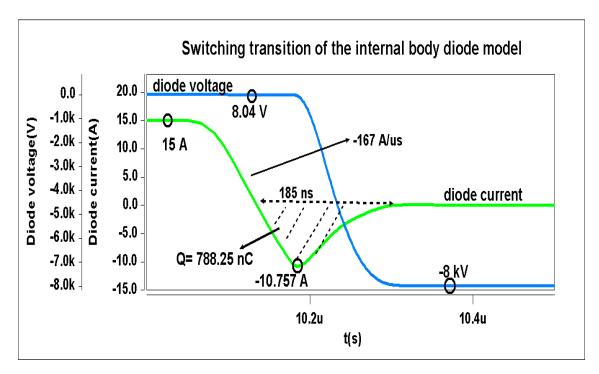

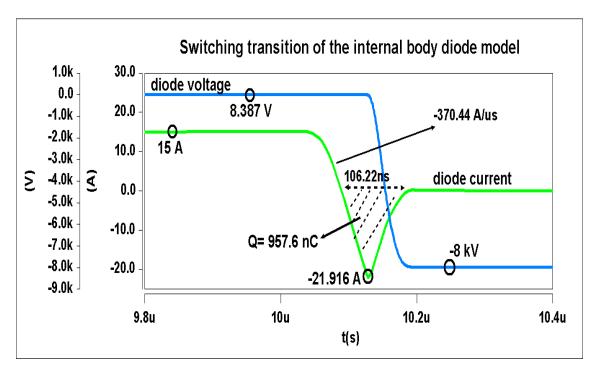

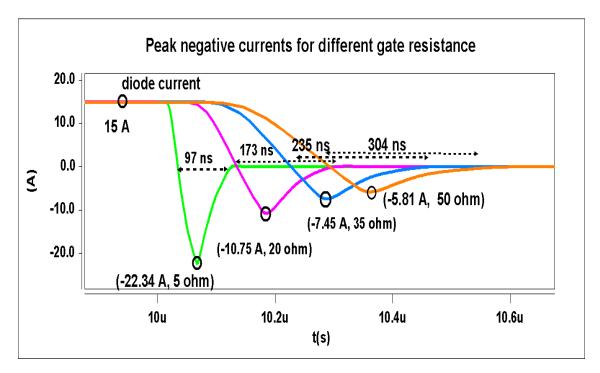

| Figure 2.30              | Switching currents and voltages in the body diode Saber model- 25 °C                                           | 38 |

| Figure 2.31              | Switching currents and voltages in the body diode Saber model- 150 °C                                          | 39 |

| Figure 2.32              | Total recovery charge $(Q_{rr})$ vs $V_{DS}$ : Saber simulation                                                | 40 |

| Figure 2.33              | Diode turn-off characteristics: Saber simulation                                                               | 41 |

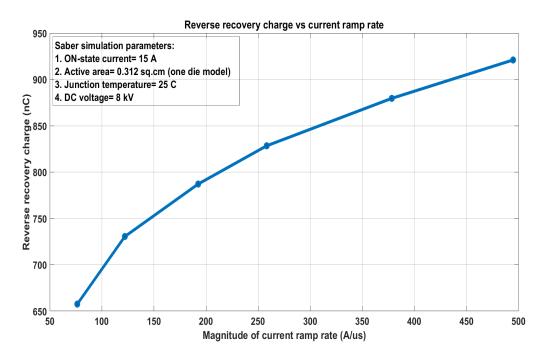

| Figure 2.34              | $Q_{rr}$ as a function of internal diode ON-State current: Saber results                                       | 44 |

| Figure 2.35              | $Q_{rr}$ as a function of di/dt: Saber results                                                                 | 44 |

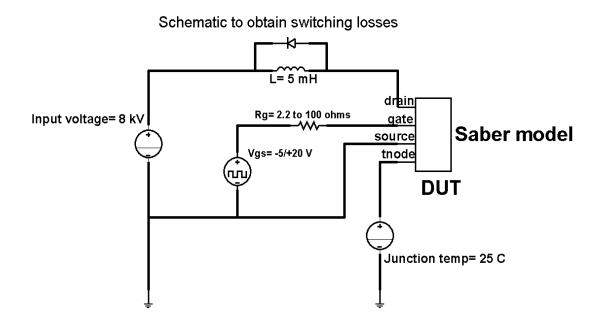

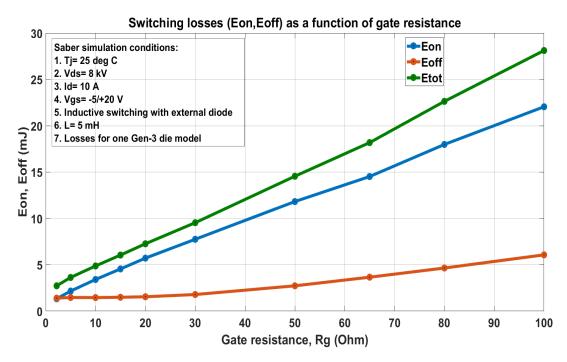

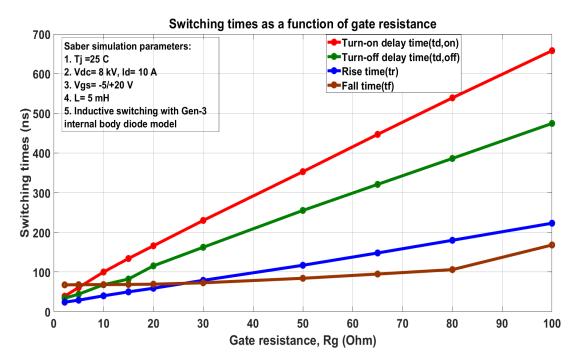

| Figure 3.1               | Switching loss schematic with inductive load and external diode                                                | 47 |

| Figure 3.2               | Switching losses with inductive load and external diode                                                        | 47 |

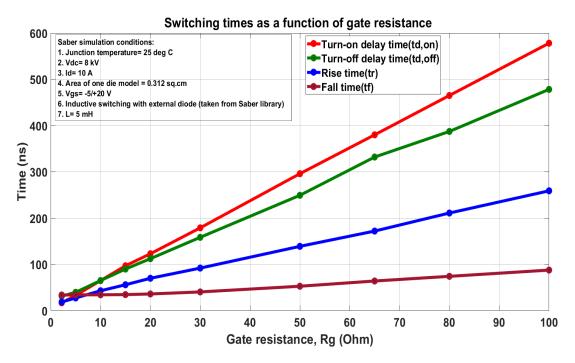

| Figure 3.3                                                                                                                                             | Switching times with inductive load and external diode                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

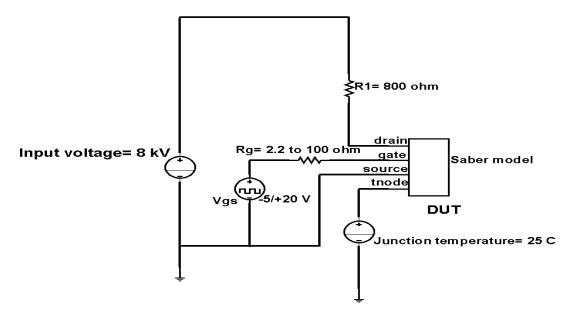

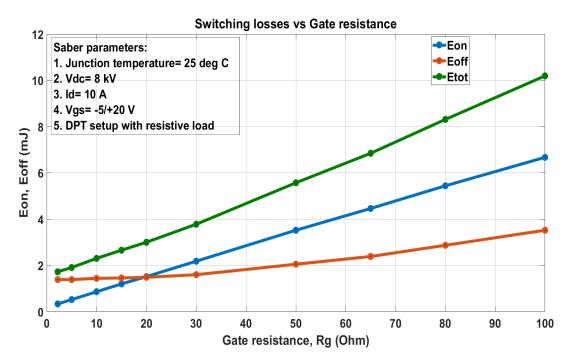

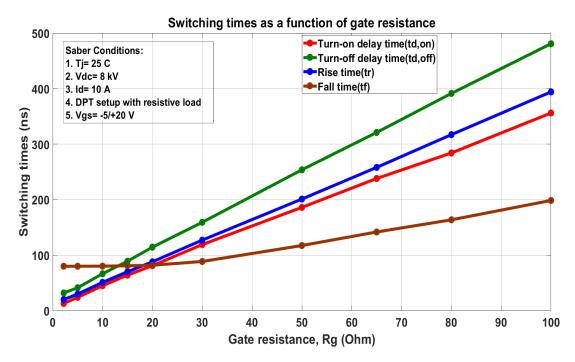

| Figure 3.4                                                                                                                                             | Switching loss schematic with resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                                                                                             |

| Figure 3.5                                                                                                                                             | Switching losses with resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                |

| Figure 3.6                                                                                                                                             | Switching times with resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                |

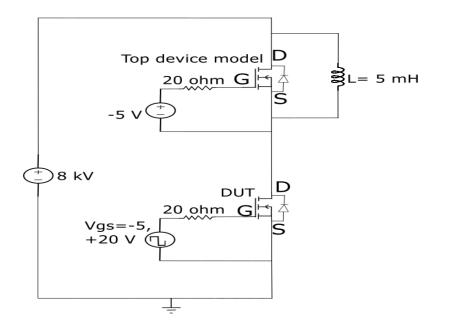

| Figure 3.7                                                                                                                                             | Switching loss schematic with half bridge configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                                                                                                                             |

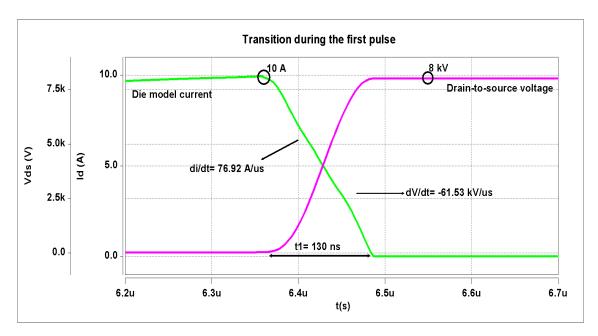

| Figure 3.8                                                                                                                                             | Switching voltage and current- with internal body diode (1 <sup>st</sup> pulse)                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53                                                                                                                                             |

| Figure 3.9                                                                                                                                             | Switching voltage and current- with internal body diode ( $2^{nd}$ pulse)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                                                                                                                             |

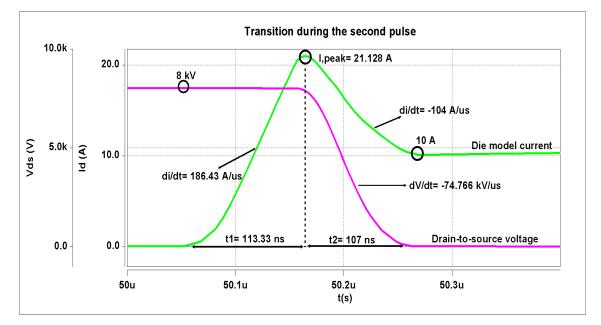

| Figure 3.10                                                                                                                                            | Switching Losses in half-bridge configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                                                                                             |

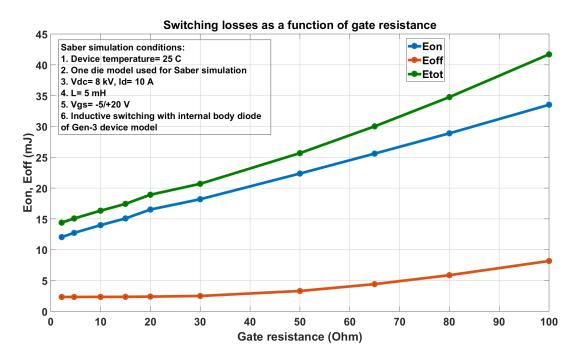

| Figure 3.11                                                                                                                                            | Switching times with the half bride configuration of internal body diode                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                                                                             |

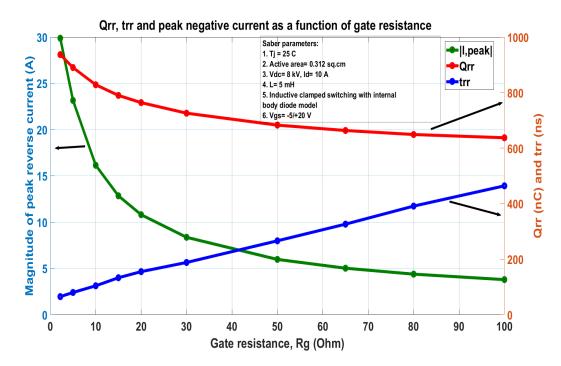

| Figure 3.12                                                                                                                                            | $Q_{rr}$ and $t_{rr}$ as a function of gate resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                                                                                                             |

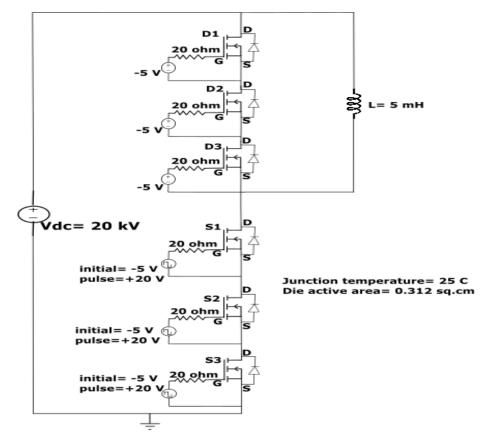

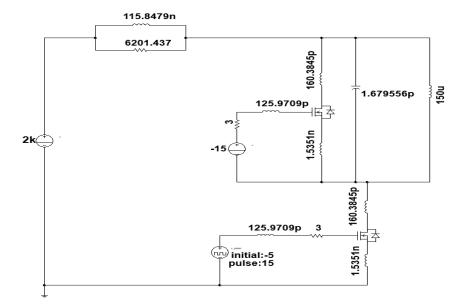

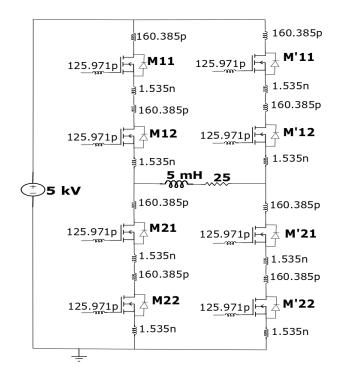

| Figure 4.1                                                                                                                                             | Double Pulse test- series connected Gen-3 MOSFET Saber models                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                                                             |

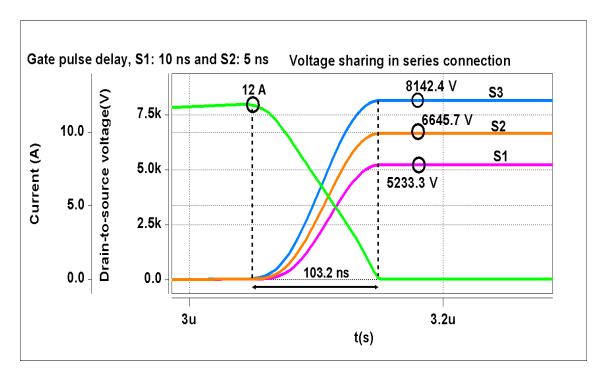

| Figure 4.2                                                                                                                                             | Voltage mismatch- DC bus voltage= 20 kV and current= 12 A                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60                                                                                                                                             |

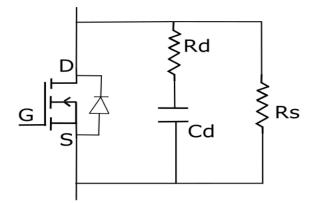

| Figure 4.3                                                                                                                                             | Balancing snubber circuit in parallel with the device model                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                             |

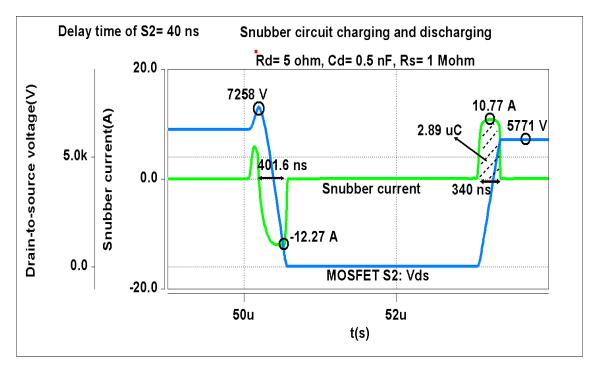

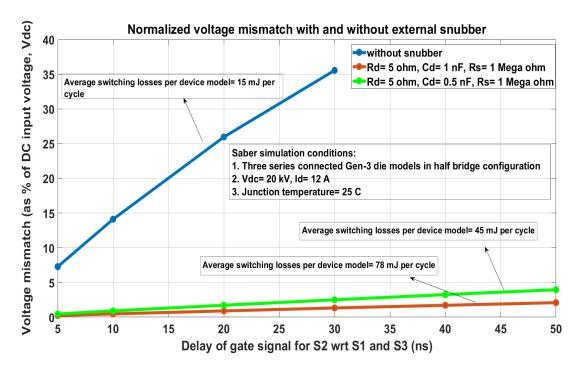

| Figure 4.4                                                                                                                                             | Snubber current and MOSFET S2 drain-to-source voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64                                                                                                                                             |

| Figure 4.5                                                                                                                                             | Voltage mismatch and switching losses with and without snubber                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                                                             |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                |

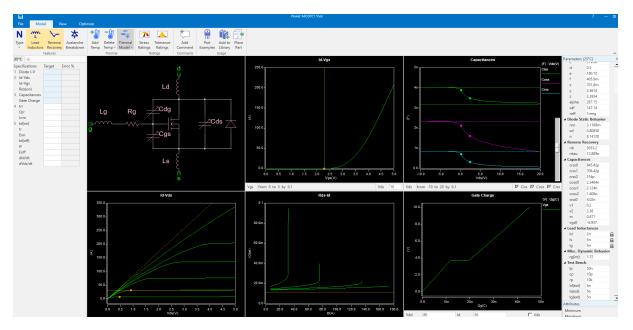

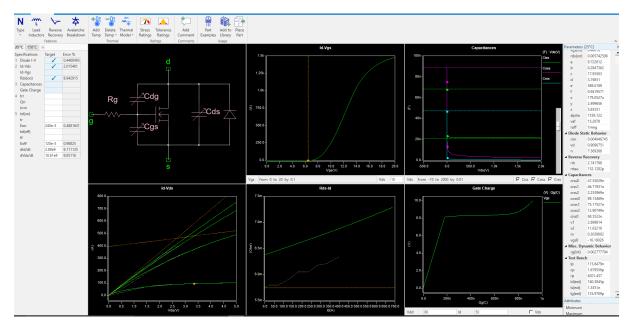

| Figure 5.1                                                                                                                                             | Saber Power MOSFET tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                             |

| Figure 5.1<br>Figure 5.2                                                                                                                               | Optimized MOSFET tool- 3.3 kV 400 A device                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                                                                                                             |

| 0                                                                                                                                                      | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in Saber                                                                                                                                                                                                                                                                                                                                                                                                                    | 69<br>69                                                                                                                                       |

| Figure 5.2                                                                                                                                             | Optimized MOSFET tool- 3.3 kV 400 A device                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69<br>69                                                                                                                                       |

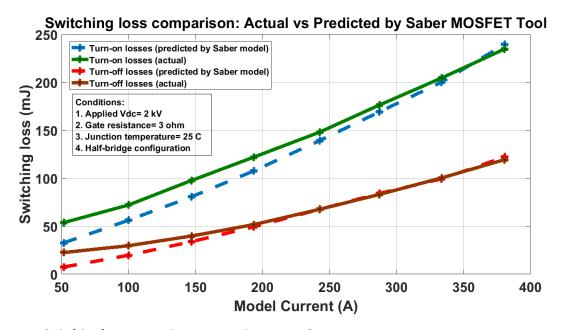

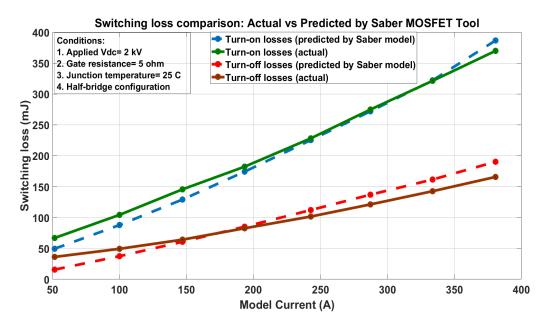

| Figure 5.2<br>Figure 5.3                                                                                                                               | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$                                                                                                                                                                                                                                                                                                       | 69<br>69<br>70<br>71                                                                                                                           |

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6                                                                                     | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$                                                                                                                                                                                                                                                                                                                                                              | 69<br>69<br>70<br>71                                                                                                                           |

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5                                                                                                   | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$                                                                                                                                                                                                                                                                                                       | 69<br>69<br>70<br>71<br>72                                                                                                                     |

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6                                                                                     | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$ Circuit used in Saber simulation                                                                                                                                                                                                                                                                      | 69<br>69<br>70<br>71<br>72<br>72                                                                                                               |

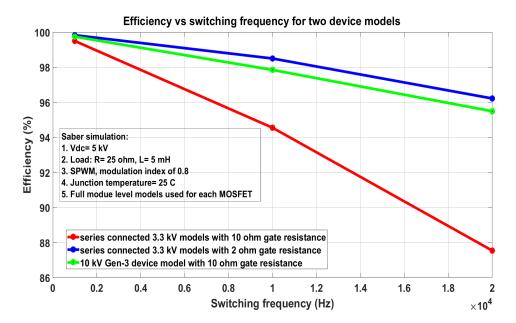

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7                                                                       | Optimized MOSFET tool- 3.3 kV 400 A device                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> </ul>                                                 |

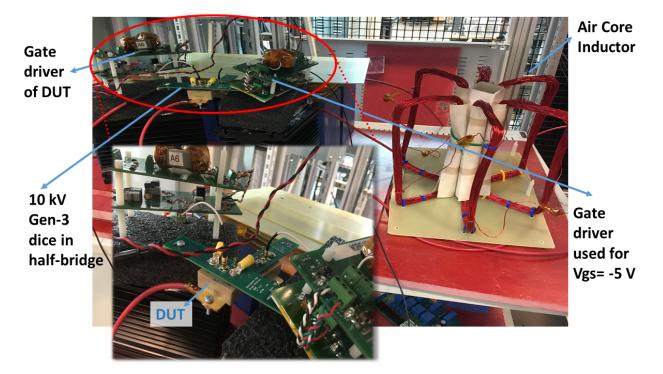

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7<br>Figure 6.1                                                         | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$ Circuit used in Saber simulationEfficiency vs switching frequency (comparison of device models)Double Pulse Test Setup5.5 kV DC bus DPT setup- Experimental vs Saber results2 kV DC bus DPT setup- Experimental vs Saber results                                                                      | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> <li>75</li> <li>75</li> </ul>                         |

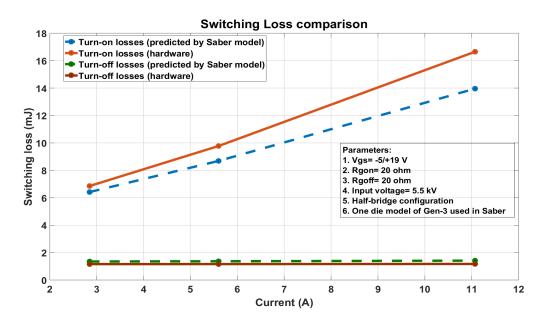

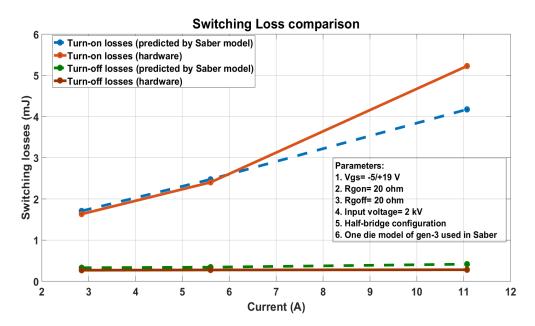

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7<br>Figure 6.1<br>Figure 6.2                                           | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$ Circuit used in Saber simulationEfficiency vs switching frequency (comparison of device models)Double Pulse Test Setup5.5 kV DC bus DPT setup- Experimental vs Saber results                                                                                                                          | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> <li>75</li> <li>75</li> </ul>                         |

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7<br>Figure 6.1<br>Figure 6.2<br>Figure 6.3                             | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$ Circuit used in Saber simulationEfficiency vs switching frequency (comparison of device models)Double Pulse Test Setup5.5 kV DC bus DPT setup- Experimental vs Saber results2 kV DC bus DPT setup- Experimental vs Saber results                                                                      | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> <li>74</li> <li>75</li> <li>76</li> </ul>             |

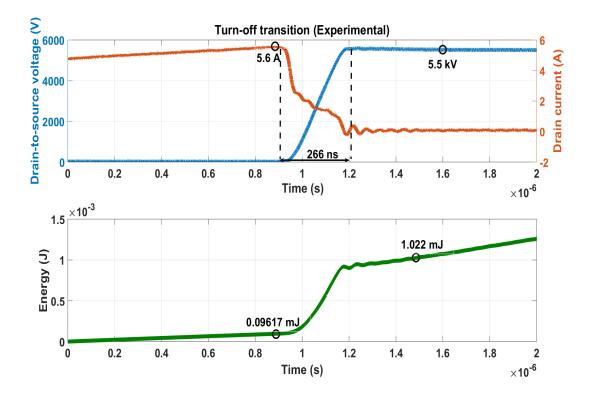

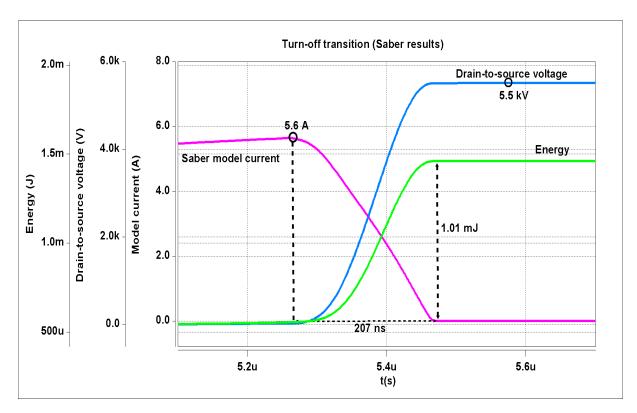

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7<br>Figure 6.1<br>Figure 6.2<br>Figure 6.3<br>Figure 6.4               | Optimized MOSFET tool- 3.3 kV 400 A deviceDouble pulse setup- 3.3 kV 400 A SiC device in SaberSwitching loss comparison- gate resistance = $3\Omega$ Switching loss comparison- gate resistance = $5\Omega$ Circuit used in Saber simulationEfficiency vs switching frequency (comparison of device models)Double Pulse Test Setup5.5 kV DC bus DPT setup- Experimental vs Saber results2 kV DC bus DPT setup- Experimental vs Saber results5.5 kV, 5.6 A, $R_g = 20 \Omega$ , turn-off transition (experimental) | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> </ul>             |

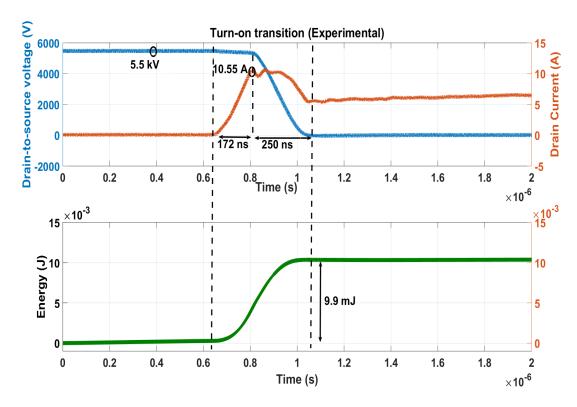

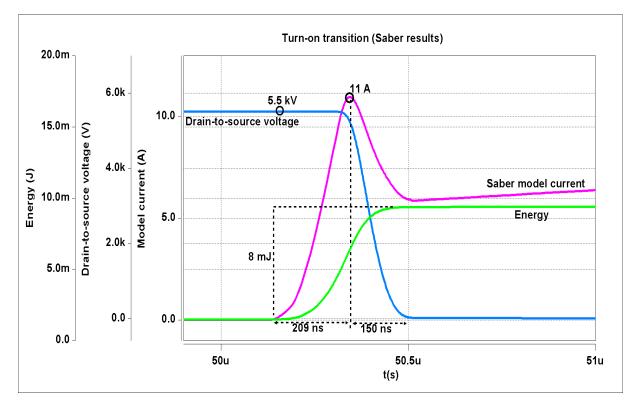

| Figure 5.2<br>Figure 5.3<br>Figure 5.4<br>Figure 5.5<br>Figure 5.6<br>Figure 5.7<br>Figure 6.1<br>Figure 6.2<br>Figure 6.3<br>Figure 6.4<br>Figure 6.5 | Optimized MOSFET tool- 3.3 kV 400 A device                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>78</li> </ul> |

# CHAPTER

1

# INTRODUCTION

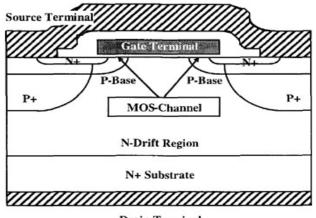

A power Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a specially designed type of device that can handle higher levels of power compared to the lateral logic-level MOSFET. To surpass the constraints on blocking voltage capability and current ratings due to the traditional planar structure, the power MOSFET was built to be vertical [2].

**Drain Terminal**

Figure 1.1 Basic Power MOSFET Structure

Consider the basic structure of a power MOSFET shown above (Figure 1.1). The presence of the lightly doped N-drift layer enables the device to block high voltages. When the device is in the blocking state, the voltage drop is supported across the P-base/N- drift junction. The ON-state resistance ( $R_{ON}$ ) of a power MOSFET is obtained by the summation of the contributions due to the channel, accumulation region, JFET region, drift region and the substrate.

$$R_{ON} = R_{CH} + R_A + R_{JFET} + R_D + R_{SUBS}$$

(1.1)

To support a higher breakdown voltage, the thickness of the drift region must be increased in proportion. This leads us to understand that the resistance contributed by the drift region  $(R_D)$  of the device would dominate over the other regions in determining the overall  $R_{ON}$  of the device. Thanks to the development of Silicon Carbide (SiC) technology in the late 1980's, there are now ways of achieving voltage ratings of the order of tens of kV for the power devices [4]. This was mainly possible by the utilizing the extremely low value of on-state resistance offered by SiC devices for the same blocking voltage. This helped in substantially reducing the device area and made it possible to manufacture SiC devices as a compact die. With regards to the specific on-resistance of the device, it is related to the breakdown voltage by the following equation:

$$R_{ON,sp} = \frac{4BV^2}{\epsilon_s \mu_n E_c^3} \tag{1.2}$$

where,  $\mu_n$  is the mobility of electrons, BV is the breakdown voltage,  $E_c$  is the critical electric field and  $\epsilon_s$  is the permittivity of Si/SiC. The critical electric field of SiC is about 10 times higher than that of silicon. This becomes the most important parameter in calculating the on-state resistance as it is raised to the third power in the equation. Substituting the values, it was found that the typical value of on-resistance of SiC is about 2000 times smaller than that of Si counterparts blocking the same voltage. Thus, silicon carbide became a great choice to fabricate power devices which required high blocking voltages. The denominator of this equation is referred to as Baliga's Figure of Merit and it directly relates the properties of the semiconductor material to the resistance of the drift region.

The energy band gap of silicon carbide is about three times (3.26 eV) higher than that of silicon (1.10 eV) thus putting it in the category of wide bandgap semiconductor. Another important advantage of using SiC for manufacturing power devices is that the leakage current at a particular temperature is much lower compared to the devices made out of Silicon [2]. The intrinsic carrier concentration of 4H-SiC is only  $6.11 \times 10^{-11} c m^{-3}$  compared to  $1.4 \times 10^{10} c m^{-3}$  of Silicon at room temperature (300 K) [2]. This clearly shows that the bulk generation current is negligible in the case of silicon carbide devices.

High power, high frequency converters that are used in motor drive applications, for example, must employ power devices that are capable of blocking high voltages and also incur lower switching

losses during their operation. Higher number of switching cycles per unit time means a better sinusoidal current output to the motor which eventually leads to reduction in the total harmonic distortion (THD) of the current. This improves system performance in terms of torque per unit ampere and efficiency. Silicon Carbide devices also provide better switching characteristics and dissipate lower energy during the switching transients. This subsequently reduces the constraints related to heatsink requirements.

#### **1.1 Motivation**

As mentioned earlier, in order to fully understand a power device and deduce its suitable applications, one has to have a good understanding of its basic characterization curves. In this thesis, a single die model of the Gen-3 10 kV 240 A SiC module is first completely characterized using the **Saber software of Synopsys**. The current rating of one die model is 18 A and is designed to have an active area of  $0.312 \ cm^2$ . To achieve the full current rating, the active area in the simulation must be increased to  $4.16 \ cm^2$ . Saber is a platform for modeling and simulating physical systems, enabling full system prototyping for applications in analog/power electronics, electric power generation/conversion/distribution and mechatronics. It is highly cross-functional as it can model systems ranging from top level mechanical blocks to digital control circuits that go as a part of a big top to bottom topology. The user has the ability to view signals through multiple levels of system hierarchy which facilitates the simulations to be carried out under one platform without the need to execute sub-system blocks using different software tools.

While characterizing the model, important plots relating to the output and transfer characteristics must be obtained to get an idea about the on-state resistance and threshold voltage of the device. The variation of these parameters with temperature needs to be analysed along with the computed value of temperature coefficients. Alongside to this work, the characteristics of an actual die are obtained from the Keysight Technologies B1505 Power Device Analyzer/Curve Tracer and compared with the results from Saber. The leakage current in the die model and the associated variations between modules is an important cause for voltage imbalance during series connected operation. This also needs to be analyzed as a function of the drain-to-source voltage to get an understanding of the blocking characteristics. To understand the switching behaviour of these devices, parasitic capacitances ( $C_{iss}$ ,  $C_{rss}$ ,  $C_{oss}$ ) needs to be extracted through small signal analysis and then plotted as a function of the drain-to-source voltage to get an inhult body diode whose forward I-V curves and reverse recovery characteristics needs to be analysed. As SiC devices can potentially operate at a higher switching frequency compared to their Si counterparts, exact computation of switching losses becomes imperative to quantitatively understand the improvement in efficiency by using the SiC device over the silicon device.

Once the characterization part is complete, the model can be evaluated in terms of its accuracy

by comparing its switching losses with the experimental values obtained from Double Pulse Test (DPT). Once the model is shown to be fairly accurate, it can then be used in the simulations of various converters to identify its advantages over other Silicon devices. The obtained simulation results can serve as motivation to build a complete model of another device at a later stage. SABER Power MOSFET tool is a great feature of the software that lets the user create a complete model of the MOSFET using non-linear curve fitting algorithms. This would be the matter of discussion at a later point in this thesis.

# **1.2** Assumptions and introduction to SABER:

The MOSFET model that is extensively characterized in this thesis is built with MAST Hardware Description Language. In the starting phase of the thesis, it was assumed that the modeling replicates the actual behaviour of the device within a reasonable range of error. After obtaining each of characterization curves, comparison was made with the plots provided by the manufacturer and the ones obtained from curve tracer. As the model predicted the parameters well, it became clear that further analysis can be done through simulation to validate more results. The work presented in this thesis is after making careful comparison with the experimental results.

Although Saber is a powerful simulation platform, with the online tutorial package currently available for the users, it may be difficult to fully tap its analysis and computational functionality. Saber can perform the following types of analyses:

- (1) DC Operating point

- (2) Small signal AC

- (3) DC Transfer

- (4) Transient

- (5) Operating point/Transient

- (6) Pole-Zero

- (7) Parametric variation

- (8) Monte Carlo

- (9) Sensitivity

- (10) Worst-Case

- (11) Experiment (nested loops of any of the above mentioned analyses)

This work primarily utilized the transient and small signal analysis features of Saber. The signal list to be generated after the analysis can be made as exhaustive as possible going to the lowest level digital control signals in a big hierarchical model. Each model in Saber is terminated by pins in the software and the waveforms at these pins can either be "across" or "through." For electrical systems, the across variable would typically be a voltage and the through signal at the pin would

typically be the current. The truncation error in the simulation should be chosen such that the error in each iteration is low. For power electronic systems, anything in the order of 10  $\mu$  to 100  $\mu$  would provide accurate results. If the switching frequency of the converter is over 20 kHz, the transition times become smaller requiring shorter time steps. Saber calculates the required time step on its own but it is useful to declare the initial time step value to avoid convergence errors. The default settings for the truncation error type would be "dynamic" and the time resolution would be 1p. Both of these can be modified by the user based on the circuit for simulation, however, it is observed that the simulator provided best results when the time resolution is decreased to 0.01p for power converters working at high switching frequencies. It is also worth noting that the simulation time might correspondingly increase with greater precision of computation. All simulation parameters and components in Saber software like resistors, capacitors, inductors are declared only as values without their associated units. The standard units of  $\Omega$ , Farad and Henry are assumed for passive elements along with seconds for the simulation times. The maximum and minimum time step overrides the default values and forces Saber to calculate multiple points even when the system convergences to a solution faster. The default algorithm for transient analysis is "Newton-Raphson" but it can be modified to "Katzenelson" to judge what works best for the specific power converter simulation. Target iteration would be the typical iteration per data point and the maximum iterations fixes the limit after which Saber displays an error. The Newton Step Density is the accuracy in each iteration and directly relates to the total simulation time of the system.

Through experience it was learnt that there were no common set of simulation settings that worked for all the converters. Based on the complexity and the type of the system, the required parameters to obtain accurate results with optimum simulation time can be understood after working with the software for a while. The following subsection provides some notes on the simulation settings used in this thesis. These parameters typically work for simulations of power converters:

#### To do a basic Operating point/Transient Analysis:

- (1) End time As required by the user.

- (2) Time Step- Typically from 1n to 0.01p.

- (3) Monitor Progress-1 (This shows the percentage of the simulation completed to the user).

- (4) Plot After Analysis- Yes (or any other option).

- (5) Signal List- Can either choose required signals/get all possible signals in the circuit.

- (6) <u>Waveforms at Pins</u>- Across/Through/Across and Through.

- (7) <u>Truncation Error</u>- Typically varies between 0.05 to 10u depending on the level of accuracy required.

- (8) Truncation Error Type- "Dynamic" by default, but can be set to the other options.

- (9) <u>Sample Point Density</u>- Varies from 10 to 1000 depending on the calculations required per iteration.

(10) <u>Time Resolution</u>- 1p is the default setting.

(11) <u>Max Time Step</u>- Can be defined by the user to limit the time step between successive iterations. Setting a smaller value increases the simulation time but does not guarantee an improvement in the accuracy.

(12) <u>Min Time Step</u>- Similar to the maximum time step, this parameter fixes the lowest time step between successive iterations.

(13) Integration Order, Integration Method- The integration method can be set to either "Gear" or "Trapezoidal". The order of the integration is set as 2 by default and generally produces better convergence than the first order option. However, the user can change to either option to check the suitability for a particular simulation.

(14) <u>Algorithm</u>- As mentioned in the previous paragraph, Newton-Raphson is the most common method for circuit simulations. If there are issues encountered with this, Katzenelson can be used.

(15) <u>Target Iterations</u>- Saber typically tries to find a solution within this specified value but increases it till the maximum specified iterations for a solution. For power converters, target iterations can be a value around 50 and the maximum can be set to 2500.

(16) <u>Newton Step Density</u>- It accounts for the accuracy in each Newtonian iteration. Higher the value, higher the simulation time.

# 1.3 Organization of Thesis

**Chapter 1:** Introduction and discussion of motivation behind doing the research detailed in this thesis work.

**Chapter 2:** Complete characterization of one 10 kV 18 A SiC die model in Saber. Comparison with the plots obtained from the Power Device Analyzer. Analysis and extraction of the following parameters/plots:

- 1. Output Characteristics ( $I_{DS}$  vs  $V_{DS}$ ) and calculation of ON-state resistance.

- 2. Transfer Characteristics ( $I_{DS}$  vs  $V_{GS}$ ) and computation of threshold voltage.

- 3. Gate-charge characteristics and evaluation of minimum gate driver power.

- 4. Discussion of Miller Effect and extraction of parasitic capacitance ( $C_{iss}$ ,  $C_{oss}$  and  $C_{rss}$ ).

- 5. Estimation of leakage current.

- 6. Analysis of body diode characteristics.

**Chapter 3:** Analysis of switching losses and comparison of delay, rise and fall times of the 10 kV device model.

**Chapter 4:** Series connection, voltage mismatch due to parameter variations and gate driver delay and design of passive RC snubber.

**Chapter 5:** Building a MOSFET model using Saber Power MOSFET tool and accuracy comparison with experimental results.

Chapter 6: Hardware validation (10 kV Gen-3 SiC MOSFET)

Chapter 7: Conclusion and future work

#### CHAPTER

2

# CHARACTERIZATION OF 10 KV DIE MODEL

In Chapter 1, the motivation and the outline of the thesis was presented along with an introduction to Saber. This chapter analyses the static and the dynamic characteristics of the die model. Saber simulation schematics and plots are provided alongside each test circuit. To understand the accuracy of the model, similar tests are carried out with the Gen-3 10 kV die on a Power Device Analyzer.

# 2.1 Output Characteristics

The output characteristics of a MOSFET is plot of the drain current  $(I_D)$  vs drain-to-source voltage  $(V_{DS})$  with the gate-to-source voltage  $(V_{GS})$  as a parameter [10]. The graph mainly consists of three regions: cut-off, active and ohmic. In the cut-off region, the applied gate-to-source voltage is lower than the threshold voltage  $(V_{TH})$ . With the maximum applied  $V_{DS}$  maintained below its rating, the current flowing through the device would be negligible. In the ohmic region, the current in the device linearly increases with the applied drain-to-source voltage. The inverse of the slope of this part of the output characteristics represents the ON-resistance of the device. The imaginary line of separation dividing the ohmic and the active region is given by the following relationship:

$$V_{GS} - V_{TH} = V_{DS} \tag{2.1}$$

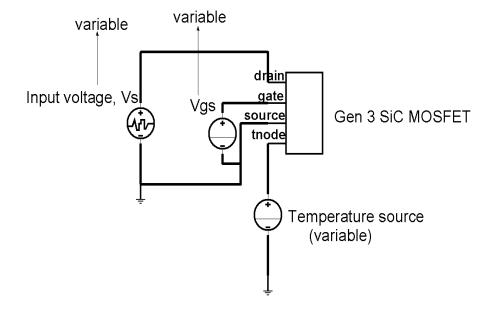

When the device is turned on ( $V_{GS} > V_{TH}$ ) and the drain-to-source voltage is less than  $V_{GS} - V_{TH}$ , the device is said to be in the ohmic region. Figure 2.2 shows the ohmic region (where current is directly proportional to the voltage drop) for  $V_{GS}$ = 15 V. On further increasing the applied voltage ( $V_{DS}$ ), the drain current does not increase steadily with the same slope but saturates at some final value. This implies that the MOSFET cannot support any more increase in current and hence presents the maximum resistance in this region. The device is now said to be in the active region of operation. The following figure shows the schematic used for simulating the output characteristics of the 10 kV SiC MOSFET model:

# Schematic to obtain Output Characteristics

Figure 2.1 Saber simulation to obtain output characteristics

The drain-to-source voltage is increased from zero with a piece-wise linear voltage source as shown above. Once the model current reaches the saturated limit, the gate-to-source voltage is increased till 19 V. The inverse of the slope of I-V characteristics is the ON-resistance of the model during operation.

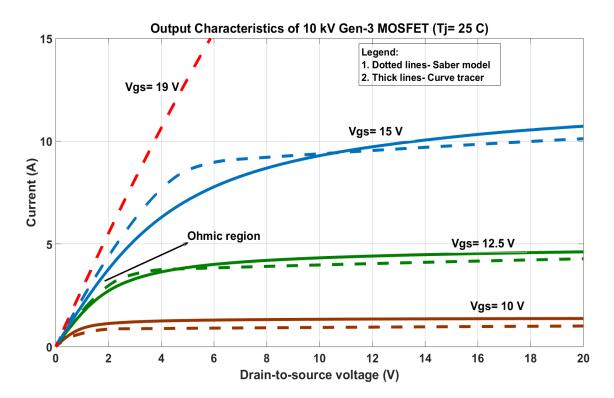

From the plot shown below (Figure 2.2), the ON-resistance at 25 °C can be calculated as  $\frac{1}{2.2328}$  = 447.86  $m\Omega$  (at  $V_{GS}$  = 15 V and  $I_D$  = 2 A). The active area used to obtain this value is at of one die of the MOSFET model. The thick lines in the plot are the corresponding values of voltages and currents obtained from the Power Device Analyzer. At the same operating point ( $V_{GS}$  = 15 V and  $I_D$  = 2 A), the

actual die exhibits a slightly higher resistance of 529.057 m $\Omega$ . At higher junction temperatures, it can be expected that the ON-resistance must increase as per the general behaviour of a power MOSFET.

Figure 2.2 Output Characteristics when junction temperature= 25 °C (Saber model vs curve tracer)

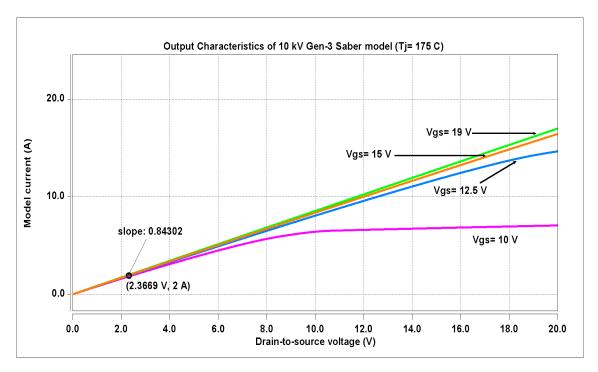

The maximum junction temperature of safe operation recommended by the manufacturer is 175 °C. At this temperature, prolonged operation might damage the device and thus in this thesis comparison between the Saber model and the results from the Power Device Analyzer is only carried out at room temperature. In addition, to get accurate results, the junction temperature has to increased and maintained at this higher temperature with a heat gun which might further introduce measurement errors due to unavoidable temperature fluctuations.

Figure 2.3 Output Characteristics when junction temperature= 175°C (Saber model)

The Saber model is simulated at a junction temperature of 175 °C as shown above (Figure 2.3). At this temperature, the ON-resistance of the MOSFET has increased to approximately 1.186  $\Omega$  at the same operating point ( $V_{GS}$  = 15 V,  $I_D$  = 2 A). Table 2.1 shows the values of  $R_{DS,ON}$  of the Saber model as a function of temperature and this clearly exhibits a positive temperature coefficient. Figure 2.4 is a graphical plot of the same data.

| S.No | Junction temperature °C | $R_{DS,ON}\left(m\Omega ight)$ |

|------|-------------------------|--------------------------------|

| 1    | 25                      | 447.86                         |

| 2    | 50                      | 511.63                         |

| 3    | 75                      | 615.006                        |

| 4    | 100                     | 740.79                         |

| 5    | 125                     | 880.049                        |

| 6    | 150                     | 1029.081                       |

| 7    | 175                     | 1186                           |

| 8    | 200                     | 1351.041                       |

**Table 2.1**  $R_{DS,ON}$  vs temperature (calculated at  $V_{GS}$ = 15 V and  $I_D$ = 2 A)- Saber model

Figure 2.4 ON- resistance  $(R_{DS,ON})$  of Gen-3 SiC MOSFET Saber model vs temperature

It is important to fully characterize the on-state resistance under different temperatures as the conduction losses incurred in power converters directly depend on these values. In situations where a particular value of efficiency must be achieved, the designer can get to know the requirements on the heatsinks to be used for the devices. Sometimes to overcome the limitations caused due to higher on-resistance, multiple devices are connected in parallel [34]. With these SiC devices providing a great reduction in  $R_{ON}$ , paralleling of multiple devices can be avoided which lowers the parts count and the assembly cost.

#### 2.2 Transfer Characteristics

This plot shows the relationship between drain current  $(I_D)$  and gate-to-source voltage  $(V_{GS})$  with the drain-to-source voltage  $(V_{DS})$  taken as the parameter. This is one of the important plots to be obtained for any device, as it helps the engineer identify the threshold voltage  $(V_{th})$  needed to get the device from the OFF state to the conduction state. This characteristic point on the graph is highly sensitive to temperature, generally following a decreasing trend as temperature increases. Thus, one would end up with a negative temperature coefficient when computing the values.

The schematic used for simulation in Saber is same as the one used to obtain the output characteristics. Instead of varying the drain-to-source voltage ( $V_{DS}$ ) to obtain changes in current ( $I_D$ ),  $V_{GS}$ is varied for a given value of  $V_{DS}$ . Three different curves are obtained for  $V_{DS}$ = 5 , 10, 15 V. The plot obtained when junction temperature  $T_j$ = 25 °C is shown below (see Figure 2.5). From Figure 2.5, it can be observed that the threshold voltage for the model is 5.85 V when the junction temperature is maintained at 25 °C. In this work,  $V_{th}$  is defined as the value of gate-to-source voltage that makes a current of 1 mA flow through the channel of one die model when the applied drain-to-source voltage is 10 V. Generally, the temperature at the junction is much higher than 25 °C due to the heat generated by switching and conduction losses in the MOSFET. Thus, in practical converter application, the device would be switched on at a voltage lower than 5.85 V. The plot obtained from curve tracer/power device analyzer is shown in Figure 2.6 and it can be seen that the threshold voltage is only 4.2 V. Thus, the threshold voltage in the Saber model is not very accurate and varies quite a lot at the defined operating point. The modelling at very low values of channel current does not accurately predict the actual behaviour of the device.

**Figure 2.5** Transfer Characteristics when  $T_j = 25 \,^{\circ}\text{C-}$  from Saber model

Figure 2.6 Transfer Characteristics when  $T_j = 25$  °C- From power device analyzer/curve tracer

On the other hand, the plots look similar for higher values of die current. The gate-to-source voltage that causes a current of 10 A in the channel is 15 V in both graphs when  $V_{DS}$  is 15 V. Similarly, annotations are made on the plots to easily check the resemblance of the Saber model with the actual characteristics. The model would have to be improved to predict the threshold voltage better. In the end of the thesis, comments on the accuracy and the shortcomings of the Saber model would be tabulated in detail. It is to be noted that the current in the actual die is limited to 10 A using the compliance factor in the power device analyzer to prevent going beyond its current rating. If needed, additional points can be extrapolated from the provided plots. The Saber model is simulated at a higher junction temperature to find the reduction in the threshold voltage.

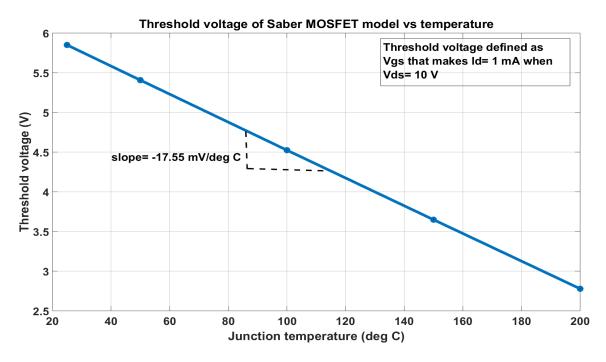

When the graph is plotted again at  $T_j = 175 \,^{\circ}$ C (refer Figure 2.7), it is observed that the model current saturates and reaches the maximum at a value of gate-to-source voltage lower than that observed at 25  $\,^{\circ}$ C. Also, the threshold voltage of the power device has decreased to 3.21 V. Simulations are carried out in Saber at multiple junction temperatures to quantitatively understand the variation of threshold voltage ( $V_{th}$ ) with respect to temperature. Figure 2.8 shows that the threshold voltage decreases almost linearly as a function of temperature. Over this range, the value of the temperature coefficient is calculated to be -17.55 mV/°C. Practically it can be expected that the Gen-3 MOSFET would exhibit a threshold value of 3 to 4 V when used in power converters taking the typical junction temperature in consideration.

Now that the Output and Transfer curves of the Gen-3 die model are obtained and compared with the actual characteristics from the curve tracer, we can shift gears into exploring the switching behaviour of the device. The next section details the method in finding the gate charge characteristics and each of the parasitic capacitance of the Saber model.

**Figure 2.7** Transfer Characteristics when  $T_j = 175$  °C (Saber model)

Figure 2.8 Variation of Threshold voltage  $(V_{th})$  with respect to temperature

#### 2.3 Gate Charge Characteristics

The gate charge characteristic is very important in starting to analyze the switching behaviour of a MOSFET. The parasitic capacitances ( $C_{iss}$ ,  $C_{oss}$  and  $C_{rss}$ ) can be used to predict a much more accurate version of the switching performance but due to the highly non-linear nature of the curves, the gate charge plot provides a simpler understanding of the turn-on/turn-off mechanisms [26]. One thing to note while using these plots is that they vary according to the test condition. For example, when the drain-to-source voltage is increased, the position of the Miller plateau voltage can slightly alter and the total value of gate charge ( $Q_G$ ) at  $V_{GS,max}$  can increase. This is because the reverse transfer capacitance  $(C_{rss})$  is function of the applied drain-to-source voltage and the value of charge obtained by integrating the C-V curve between the switching conditions change with  $V_{DS}$ . Conversely, the total value of  $Q_G$  would reduce when the applied drain-to-source voltage is reduced. Generally, the gate charge characteristic does not vary much with the device current and stays constant from the threshold value to the rated value. To obtain this characteristic, a simple test circuit of the SiC MOSFET model driving a resistive load would suffice. Apart from predicting the switching behaviour, the gate charge curve can provide an understanding of the gate driver requirements of the device under test (DUT). The amount of charge required for the total input equivalent capacitance  $(C_{eq})$  must be delivered by the driver during turn-on. The same amount of charge needs to be withdrawn from the capacitances to completely turn-off the device. The driver's ability to do both of these actions per unit time determines its minimum power rating for satisfactory performance. The gate drive power can be computed by the following relationship:

$$P_{drv} = Q_{gate} \times freq \times \Delta V_{Gate} \tag{2.2}$$

where,

$Q_{gate}$  is the total charge required for the turn-on process freq is the switching frequency of the gate driver and  $\Delta V_{Gate}$  is the gate driver voltage swing

For the simulation in Saber, the gate charge was computed as a time integral of the gate current (output current of the gate driver) and plotted as a function of the gate to source voltage ( $V_{Gate}$ ). Even though a constant gate current can be used to simplify the analysis, this work computes the time integral with the corresponding instantaneous values obtained from Saber (see equation 2.3). By following this procedure, it was observed that the total charge fairly remained constant for different values of drain current ( $I_D$ ).

$$Q_{gate} = \int_{0}^{t_{ON}} I_{gate} dt \tag{2.3}$$

As shown in equation 2.3, the integration is carried out from the time of switching ON the driver (assumed to be t=0) until the time required to deliver the charge to the MOSFET model for complete turn-on. The time elapsed is called the turn-on time ( $t_{ON}$ ). The maximum gate drive current is computed by dividing the highest gate drive voltage swing and the lowest gate resistance that can be used for the power MOSFET.

$$I_{drv,max} = \frac{\Delta V_{Gate}}{R_{Gate,min}}$$

(2.4)

In practical situations, the gate circuit includes some inductance in the loop and the maximum current rise is also limited by this parasitic inductance. The equivalent can be represented as a series RLC circuit by considering the device capacitance as  $C_{eq}$  during turn-on. The solution considering non-oscillating gate current yields that the maximum current of the gate driver is 0.7 times the value calculated from equation 2.4 [14]. All of these results can now be utilized in calculating the driver power required for the Gen-3 device model.

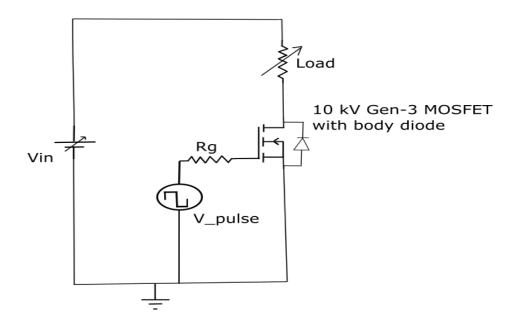

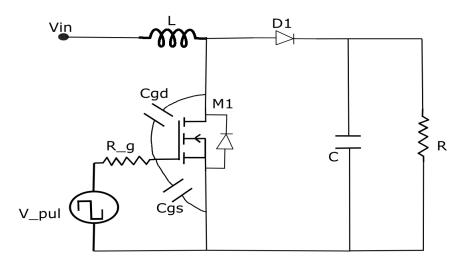

Figure 2.9 Simulation Schematic to obtain gate charge characteristics

The schematic (Figure 2.9) shown for the simulation uses the 10 kV Gen-3 device driving a resistor. The value of  $V_{in}$  decides the drain-to-source voltage swept between the ON and the OFF states. The value of  $R_G$  is 20  $\Omega$  in the simulation. The drain current is arbitrarily chosen to be 10

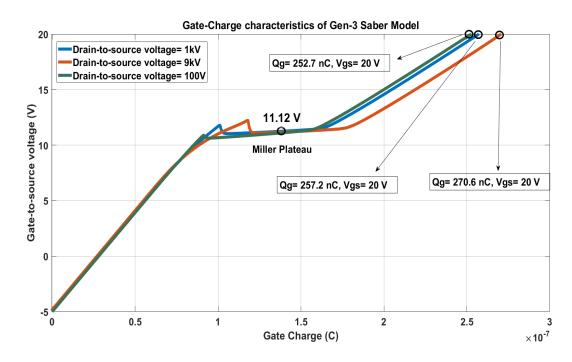

A. The charge flowing through the gate terminal of the MOSFET is obtained by integrating the current during the turn-on transition. From the plot (Figure 2.10), it is evident that the gate voltage increases steadily until it reaches the Miller plateau at about  $V_{gp} = 11.1$  V. At this point, the gate current gets diverted into the Miller capacitance ( $C_{gd}$ ) and the incoming charge is used to charge this capacitance. Crossing the Miller plateau, the gate-to-source voltage increases again until the total gate charge is sufficient enough to fully turn on the device.

Figure 2.10 Gen-3 Saber device model: gate charge characteristics

To reiterate to the reader, this plot is the characteristic for just one die model (rated 18 A) which has an active area of 0.312  $c m^2$ . To obtain the characteristics of the entire module (rated 240 A), several of these dice have to be connected in parallel or the active area must be increased to 4.16  $c m^2$  in the simulation. It is observed from the above plot that the total gate charge required when  $V_{GS}$  reaches 20 V is 271 nC when  $V_{in}$  ( $V_{DS}$ ) is 9 kV. The total change in the gate voltage is 20 - (-5) = 25 V. The value of the required gate charge is slightly short of 253 nC when  $V_{DS}$  is decreased all the way to 100 V. The subtle difference is caused by the area under  $C_{rss}$ -  $V_{DS}$  graph from 100 V to 9 kV. Assuming that the Gen-3 die is operated in a converter running at 20 kHz, the minimum gate driver power predicted by the model is:

$$P_{drv,min} = 271nC \times 25V \times 20kHz = 135.5mW \tag{2.5}$$

This value would have to be multiplied by the number of dice used in parallel to obtain the overall rating of the driver. Likewise, the peak current capability is computed for a minimum gate resistance of  $2\Omega$ .

$$I_{drv,max1} = \frac{25}{2} = 12.5A \tag{2.6}$$

With the reduction factor of 0.7, the peak value becomes,

$$I_{drv,max} = 12.5 \times 0.7 = 8.75A \tag{2.7}$$

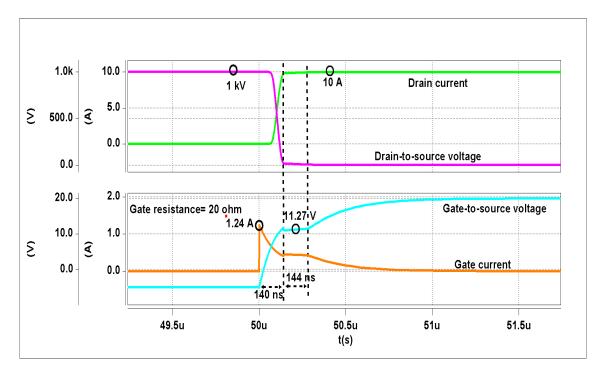

The turn-on transition plots obtained from Saber while simulating the schematic are shown in Figures 2.11 and 2.12. The input voltage is changed from 1 kV to 9 kV with other parameters remaining the same. The device model is switched ON at time t= 50  $\mu$ s by applying a gate-to-source voltage. Since the switching is done with a resistive load, the transients (di/dt and dV/dt) happen simultaneously. It should be noted that the model current settles at 10 A without any overshoot in this case. The gate-to-source voltage increases steadily from -5 V to about 11 V where it hits the characteristic Miller plateau as shown in Figure 2.11. The initial spike in the gate current when  $R_G = 20 \Omega$  is 1.25 A. The time required to hit the Miller plateau would increase as the value of  $V_{DS}$ increases to supply the extra gate charge. For the Gen-3 MOSFET die model, this time ranges from 120 ns to 200 ns for the first transition. For both the 1 kV and 9 kV case, the second transition time is fairly the same after which the gate current begins to drop exponentially.

Saber predicts that the gate driver would have to provide 3.6  $\mu$ C of charge to drive the whole module (10 kV, 240 A) of Gen-3. To use the module in a power circuit switching at 20 kHz, the minimum power rating of the driver should be approximately 2 W.

**Figure 2.11**  $V_{DS}$ ,  $I_D$ ,  $V_{GS}$  and  $I_G$  when  $V_{in} = 1$  kV, current= 10 A and  $R_G = 20 \Omega$  (Saber model)

**Figure 2.12**  $V_{DS}$ ,  $I_D$ ,  $V_{GS}$  and  $I_G$  when  $V_{in} = 9$  kV, current= 10 A and  $R_G = 20 \Omega$  (Saber model)

#### 2.3.1 Miller Effect and estimation of gate charging time

For the Gen-3 MOSFET die model, it was observed that the required gate charge to completely turn-on the device varied quite a bit depending on the applied drain-to-source voltage. This section details analysis on how the Miller effect decides the equivalent capacitance during turn-on and the time required to completely turn on the 10 kV die model. Even for a very low value of  $C_{rss}$ , the gate driver "sees" a much larger value as it gets multiplied by a factor of  $\frac{V_{DS}}{V_{GS}}$  due to Miller Effect. Consider the following discussion,

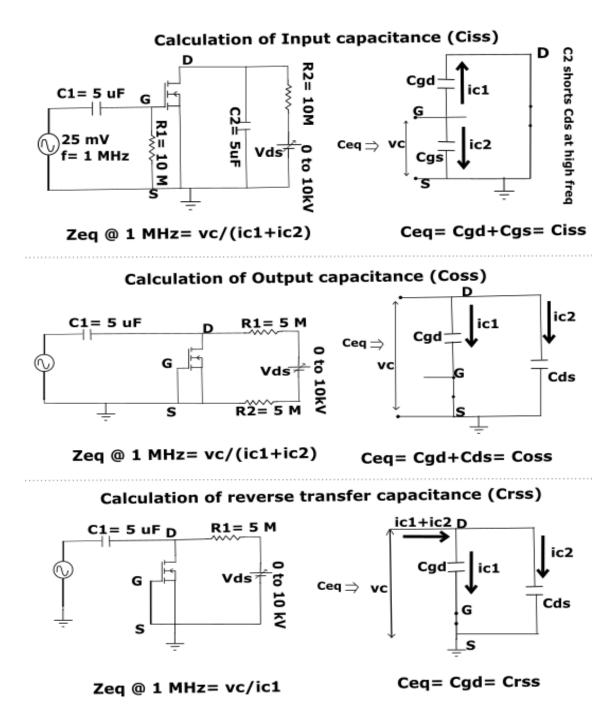

Figure 2.13 Schematic- equivalent capacitance

The total equivalent capacitance can be derived by taking the ratio between the total amount of charge delivered during turn-on and the total change in the value of gate-to-source voltage. Let the values of  $V_{GS}$  before turn-on be  $V_{GS,min}$  and that after complete turn-on be  $V_{GS,max}$ . Similarly, let the blocking voltage during turn-off be  $V_o$  and the ON-state voltage be zero (ideal case). Thus, the voltage change across  $C_{gs}$  is  $V_{GS,max} - V_{GS,min}$  and that across  $C_{gd}$  would be  $V_o + V_{GS,max} - V_{GS,min}$ . For simplicity in representation, let the total change in the gate-to-source voltage be represented by  $V_{GS}$ . Thus,

$$C_{eq} = \frac{Q_{tot}}{V_{GS}} \tag{2.8}$$

Also the total charge is the sum of the charges present in  $C_{gs}$  and  $C_{gd}$ ,

$$Q_{tot} = V_{GS}C_{gs} + (V_{GS} + V_o)C_{gd}$$

(2.9)

Substituting equation 2.9 in 2.8, we obtain

$$C_{eq} = C_{gs} + C_{gd} \left(1 + \frac{V_o}{V_{Gs}}\right) \tag{2.10}$$

Equation 2.10 clearly shows the boost due to Miller effect on the gate-to-drain capacitance. Assuming the ideal case of a constant gate current  $I_g$ , one can write the following equation,

$$t_{on} = \frac{C_{eq} V_{GS}}{I_g} \tag{2.11}$$

where  $t_{on}$  represents the gate charging time. A more realistic estimation of the charging time is to consider the equivalent circuit shown in Figure 2.14. " $V_{pul}$ " provides an ideal source of PWM pulse and acts like a step input to the R-C circuit during turn-on. The voltage across the equivalent capacitor is the gate-to-source voltage across the MOSFET as indicated. To reach about 98 % of the applied voltage, the elapsed time is about 4 time constants. From mutiple iterations of simulation in Saber, it is observed that " $Q_{tot}$ " varies from 250 nC to 275 nC as  $V_{DS}$  is increased till the rated value. Using equation 2.8, the maximum value of  $C_{eq}$  is found to be 11 nF. Thus, the time constant of the charging circuit for a value of 20  $\Omega$  gate resistance would be 220 ns. Thus the model predicts that the 10 kV Gen-3 device would take about 900 ns until the parasitic capacitances are fully charged with a gate resistance of 20  $\Omega$ . In the next section, a detailed method for finding the parasitic capacitance ( $C_{iss}$ ,  $C_{oss}$  and  $C_{rss}$ ) of the model is derived through small signal analysis. The test is also performed with the device in the curve tracer and the values are compared as a function of  $V_{DS}$ .

Figure 2.14 Equivalent circuit representation during turn-on

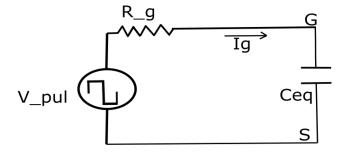

#### 2.4 Parasitic Capacitances