#### **ABSTRACT**

KADAVELUGU, ARUN KUMAR. Medium Voltage Power Conversion Enabled by 15 kV SiC IGBTs. (Under the direction of Dr. Subhashish Bhattacharya).

This work is aimed at experimental evaluation of the state-of-the-art 15 kV SiC IGBTs with the ultimate objective of demonstrating them on medium voltage, high frequency power conversion systems, and investigating techniques for their optimal utilization. As the experimental switching characteristics of the 15 kV SiC N-IGBTs have never been reported, the foremost step to understand the SiC IGBTs was to build a high voltage inductive switching test setup to characterize the 15 kV SiC IGBTs up to 11 kV. The 5 µm field-stop buffer layer N-IGBTs have been found to be more suitable than 2 µm buffer layer N-IGBTs for high frequency power conversion, due to their lower turn-off energy loss and turn-on dv/dt. However, both variants of the N-IGBT have exhibited two-slope switching voltage transitions with steeper transitions over punch-through voltage.

This led to in-house development of high dv/dt immunity, high isolation gate driver for the SiC IGBTs, as the commercially available gate drivers are not capable of handling such high stress. The gate driver has been tested on pulse tests up to 11 kV and over 100 kV/ $\mu$ s. This was followed by evaluation on continuous switching tests by developing different converter circuits to expose the gate driver to 8 kV and 85 kV/ $\mu$ s.

Subsequently, the 15 kV, 5 µm buffer layer SiC N-IGBTs have been evaluated on 10 kV hard-switched boost converter heat-run tests with power dissipation density of 550 W/cm<sup>2</sup> (active area) at the junction temperature of 146°C. This boost converter has been used as a 10 kV dc power source for the subsequent tests. A method to accurately measure the online IGBT junction temperature based on turn-off voltage waveform is provided. The hard-switching frequency limits have been analytically evaluated based on the switching data and thermal resistance of the IGBT module package.

Following the gate driver evaluation and IGBT heat-run tests, a three-level neutral point clamped converter has been developed, and tested up to 10 kV dc input at 10 kHz and 9 kW resistive loading. After this, the IGBTs have been demonstrated on 10 kV, two-level, H-bridge inverter at 5 kHz and 6 kW. This was followed by evaluating 15 kV, multi-chip IGBT

modules and comparing their performance with single-chip IGBT modules. Using the multichip IGBT co-pack modules, six three-level poles have been built and validated up to 10 kV dc input, for a three-phase solid state transformer application.

The latter part of the work is focused on extracting optimal performance of the SiC IGBTs for converter applications. The dv/dt of the IGBTs has been investigated with respect to current, temperature and buffer layer thickness. Analytical results of the dv/dt and their comparison with the experimental data are presented for the turn-off dv/dt over punch-through. The passive gate current control technique has been used to reduce the turn-on dv/dt. However, this led to drastic increase in turn-on energy loss, which was addressed by implementing a two-stage active gate driver at 11 kV.

Subsequently, the discrete SiC IGBTs have been evaluated under zero voltage switching (ZVS) conditions using a capacitive snubber. The influence of the voltage spike during ZVS turn-on and the turn-off current bump have been provided. The 5 µm buffer layer IGBTs are found to be better from the perspective of percentage turn-off energy loss reduction, in comparison to the 2 µm buffer layer IGBTs. Lastly, complementary inverter topology using 15 kV P-IGBT and N-IGBT has been investigated for zero dv/dt stressed gate drivers.

© Copyright 2015 by Arun Kumar Kadavelugu All Rights Reserved

#### Medium Voltage Power Conversion Enabled by 15 kV SiC IGBTs

#### by Arun Kumar Kadavelugu

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

**Electrical Engineering**

Raleigh, North Carolina

2015

APPROVED BY:

| Dr. Subhashish Bhattacharya<br>Committee Chair | Dr. B. Jayant Baliga |  |

|------------------------------------------------|----------------------|--|

|                                                |                      |  |

|                                                |                      |  |

| Dr. Iqbal Husain                               | Dr. Xiangwu Zhang    |  |

# **DEDICATION**

To my Parents and Brothers

#### **BIOGRAPHY**

Arun Kumar Kadavelugu was born in Korapally, Karimnagar district, of the state of Andhra Pradesh in India. He received his Bachelor of Engineering in Electrical Engineering from Osmania University campus, in 2005. He completed his Master of Technology in Electrical Engineering from Indian Institute of Technology in 2007, with specialization in Power Electronics. From 2008 to 2009, he worked on a standalone renewable system implementation project sponsored by the government of India. In 2009, he joined the Future Renewable Electric Energy Development and Management (FREEDM) systems center, Department of Electrical and Computer Engineering, North Carolina State University to pursue his PhD. His research interests are power conversion using wide band-gap devices, which include 1200 V SiC MOSFETs, 10 kV SiC MOSFETs and 15 kV SiC IGBTs. He worked as an R&D Intern at GE Global Research, Niskayuna, during fall 2011.

#### **ACKNOWLEDGMENTS**

Several people have helped me directly or indirectly during the course of my PhD. I am very thankful to each and every one of them. Pardon me, if I have forgot to mention someone explicitly.

Firstly, I take this opportunity to thank my supervisor Prof. Subhashish Bhattacharya for giving me enormous freedom in choosing my work, for his kind support and encouragement, and most importantly for entrusting challenging and exciting responsibilities on me.

I am very grateful to Prof. Jayant Baliga for taking his valuable time to explain the fundamentals of device physics, for the several discussions on the SiC IGBT characteristics, and for the critical comments on my work. I am very thankful to Prof. Iqbal Husain and Prof. Xiangwu Zhang for their kindness in accepting my request to be on my PhD committee, and for the enormous support they provided.

I am extremely thankful to Dr. N. Ravisekhar Raju at GE Global Research for his valuable suggestions on high voltage experiments, his kind encouragement and several hours of discussions during and post my internship with GE. I am very thankful to Dr. Sei-Hyung Ryu at Cree for taking his valuable time to explain me the behavior of the SiC IGBTs and for providing several practical insights on the IGBT characteristics. I am very grateful to Dr. Scott Leslie at Powerex for his several email exchanges explaining the intricacies of high voltage packaging. I thank Mr. Mark Miller at Eaton for his valuable mentoring during my initial years of PhD.

I need to specially mention my colleagues Gangyao, Arvind, Kamalesh, Sachin, Awneesh, Xu, Fei, Seunghun, Dhaval, Krishna, Ankan, Ritwik, Hesam, Sayan, Edward, Meng-Chia and Woongje for several insightful discussions. I am grateful to Harekrishna, Krishnan Subramanian and Sameer Khan for their help in mechanical design of the high voltage converter prototypes. I am thankful to our lab manager Hulgize for his valuable help in

mechanical design of the converters and for guidance on high voltage safety. I thank our receptionist Karen Autry for her prompt help in component orders.

The invaluable support and encouragement provided my roommates and their spouses is highly appreciated. My special thanks to Prasenjit, Ajay-Sandhya, Boopathy-Vijji, Samir-Swastika, Kasu-Jayashree, Kiran and Hemanth. I thank all my friends from Osmania University, IIT Kanpur and FREEDM center for their encouragement.

Finally, the immense support and guidance from my family has been a very great help. Their critique of my career choices and their toleration have an important role. It needs a special mention that my father and younger brother have motivated me to work hard.

# TABLE OF CONTENTS

| LIST OF TABLES                                                  | ix |

|-----------------------------------------------------------------|----|

| LIST OF FIGURES                                                 | X  |

| Chapter 1: Introduction                                         | 1  |

| 1.1 Background                                                  | 1  |

| 1.2 Outline of this Dissertation                                | 2  |

| Chapter 2: Hard Switching Characterization of 15 kV SiC N-IGBTs | 4  |

| 2.1 Introduction                                                | 4  |

| 2.2 The 15 kV SiC N-IGBT                                        | 4  |

| 2.3 Hard-switching Characteristics                              | 6  |

| 2.3.1 Clamped-Inductive Load Switching Conditions               | 6  |

| 2.3.2 Partly Inductive Load Switching Conditions                | 11 |

| 2.3.3 Resistive Load Switching Conditions                       | 13 |

| 2.4 Comparison of 15 kV 5 μm and 2 μm buffer layer N-IGBTs      | 15 |

| 2.5 Power Converter Design Considerations                       | 18 |

| 2.6 Summary                                                     | 20 |

| Chapter 3: Gate Driver Development for 15 kV SiC N-IGBT         | 21 |

| 3.1 Introduction                                                | 21 |

| 3.2 Gate Driver Development                                     | 22 |

| 3.2.1 Design Criteria                                           | 22 |

| 3.2.2 High Isolation Power Supply Design                                          | 23   |

|-----------------------------------------------------------------------------------|------|

| 3.2.3 The Driver Stage Development                                                | 27   |

| 3.3 Experimental Validation                                                       | 28   |

| 3.4 Robustness Evaluation of the Gate Driver                                      | 35   |

| 3.5 Summary                                                                       | 41   |

| Chapter 4: Demonstration of 15 kV SiC N-IGBT based Power Converters               | 42   |

| 4.1 Introduction                                                                  | 42   |

| 4.2 Thermal Resistance of the SiC IGBT Module                                     | 42   |

| 4.3 Analytical Evaluation of IGBT Frequency limits based on the Experimental Data | a46  |

| 4.4 Demonstration of the IGBT Frequency Capability on a 10 kV Boost Converter     | 51   |

| 4.5 Three-level, 10 kV, NPC Converter Demonstration                               | 56   |

| 4.6 Two-level, 10 kV, H-bridge Converter Demonstration                            | 61   |

| 4.7 Evaluation and Demonstration of multi-chip 15 kV N-IGBT Modules               | 64   |

| 4.8 Summary                                                                       | 69   |

| Chapter 5: Understanding dv/dt of 15 kV SiC N-IGBTs and Active Gate Control       | ol71 |

| 5.1 Introduction                                                                  | 71   |

| 5.2 Understanding dv/dt of 15 kV SiC N-IGBTs                                      | 71   |

| 5.2.1 Turn-off Transition at 11 kV, 10A and 25°C                                  | 72   |

| 5.2.2 dv/dt with Current Variation at 11 kV and 25°C                              | 74   |

| 5.2.3 dv/dt with Increased Field-stop Buffer Layer Thickness                      | 78   |

| 5.2.4 dv/dt with Temperature                                                      | 81   |

| 5.3 Active Gate Current Control of 15 kV SiC N-IGBT                       | 84  |

|---------------------------------------------------------------------------|-----|

| 5.4 Summary                                                               | 91  |

| Chapter 6: Design Considerations for 12 kV SiC IGBTs based ZVS Converters | 92  |

| 6.1 Introduction                                                          | 92  |

| 6.2 ZVS Turn-on Characteristics                                           | 92  |

| 6.3 ZVS Turn-off Characteristics                                          | 94  |

| 6.4 Considerations for Power Converter Design                             | 99  |

| 6.5 Summary                                                               | 100 |

| Chapter 7: Complementary Inverter Using 15 kV P-IGBT and N-IGBT           | 101 |

| 7.1 Introduction                                                          | 101 |

| 7.2 Characteristics of 15 kV, 5 A, P-IGBT                                 | 103 |

| 7.3 Characteristics of 15 kV, 5 A, N-IGBT                                 | 106 |

| 7.4 Discussion                                                            | 108 |

| 7.5 Experimental Results                                                  | 110 |

| 7.6 Summary                                                               | 114 |

| Chapter 8: Conclusions                                                    | 115 |

| 8.1 Summary of the Work                                                   | 115 |

| 8.2 Scope for Future Research                                             | 116 |

| REFERENCES                                                                | 118 |

| APPENDIX                                                                  | 121 |

## LIST OF TABLES

| Table 2.1: Inductive turn-off energy loss at 10 kV, 5 A and 10 A                                                   | 10  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: Turn-on energy loss variation of 15 kV N-IGBT with temperature                                          | 11  |

| Table 2.3: dv/dt of 2 μm and 5 μm IGBTs at 10 kV, 8 A (turn-on) and 10 A (turn-off)                                | 17  |

| Table 2.4: Energy loss values of 15 kV, 2 μm and 5 μm SiC IGBTs                                                    | 18  |

| Table 3.1: Specification of the different cores evaluated for the high isolation transformer                       | 25  |

| Table 3.2: Summary of gate driver evaluation.                                                                      | 34  |

| Table 3.3: Comparison of the isolation stage transformers used for dv/dt performance evaluation                    | 39  |

| Table 4.1: Temperature drop across each layer in the thermal path of the 15 kV SiC IGB module package              |     |

| Table 4.2: Parameters of 15 kV SiC N-IGBT used for evaluating hard-switching limits                                | 47  |

| Table 4.3: Summary of hard switching frequency limits of the 15 kV SiC N-IGBT                                      | 50  |

| Table 4.4: Summary of boost converter demonstration                                                                | 54  |

| Table 4.5: Voltage stress across baseplate isolation of each device in the 3-level NPC po with reference to ground |     |

| Table 5.1: dv/dt of 2 μm and 5 μm IGBTs at 10 kV, 8 A (turn-on) and 10 A (turn-off)                                | 81  |

| Table 5.2: Parameters used in the analytical evaluation                                                            | 83  |

| Table 6.1: Turn-off energy loss of the SiC IGBTs                                                                   | 100 |

| Table 7.1: Comparison of 15 kV, P-IGBT and N-IGBT at 6 kV, 5 A                                                     | 109 |

## LIST OF FIGURES

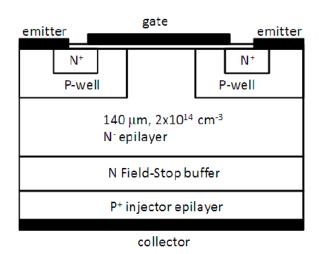

| Fig. | 2.1:  | Simplified cross-sectional view of 15 kV SiC N-IGBT                                                                  | 5  |

|------|-------|----------------------------------------------------------------------------------------------------------------------|----|

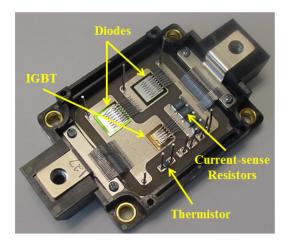

| Fig. | 2.2:  | 15 kV SiC N -IGBT co-pack module                                                                                     | 5  |

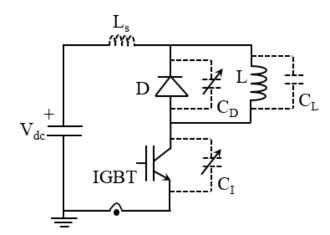

| Fig. | 2.3:  | The double-pulse test circuit schematic with different parasitic components                                          | 6  |

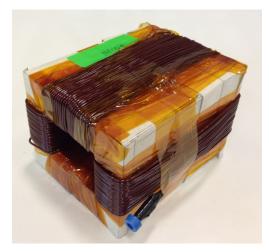

| Fig. | 2.4:  | The high voltage, low capacitance, HV load inductor                                                                  | 7  |

| Fig. | 2.5:  | Turn-on and turn-off energy loss values with current variation at 10 kV and 25°C, under clamped inductive load       | 8  |

| Fig. | 2.6:  | Turn-off switching transitions at 10 kV, 25°C, 5 A and 10 A, under clamped inductive load conditions                 | 8  |

| Fig. | 2.7:  | Turn-off switching loss variation with temperature at 5 A and 10 A at 10 kV, under clamped inductive load conditions | 9  |

| Fig. | 2.8:  | Turn-off switching transitions with temperature at 10 kV and 10 A, under clamped inductive load conditions           | 9  |

| Fig. | 2.9:  | The turn-on energy loss variation of 15 kV N-IGBT with temperature with $R_{G(ON)}$ = 33 $\Omega$                    | 11 |

| Fig. | 2.10: | Comparison of turn-on transitions with L and RL loads at 10 kV and 5 A, at 25°C                                      | 12 |

| Fig. | 2.11: | Comparison of turn-off transitions with L and RL loads at 10 kV and 5 A, at 25°C                                     | 13 |

| Fig. | 2.12: | Comparison of turn-on transitions with L and R loads at 10 kV and 5 A, at 25°C                                       | 14 |

| Fig. | 2.13: | Comparison of turn-off transitions with L and R loads at 10 kV and 5 A, at 25°C                                      | 14 |

| Fig. | 2.14: | Comparison of turn-on energy loss with L, RL and R loads at 10 kV and 25°C                                           | 15 |

| Fig. | 2.15: | Comparison of turn-off energy loss with L, RL and R loads at 10 kV and 25°C                                                               | 15   |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. |       | Turn-off transitions of 15 kV, 2 $\mu m$ and 5 $\mu m$ thick buffer layer, SiC IGBT at 10 kV, 10 A, 25°C with $R_{G(OFF)}$ of 10 $\Omega$ | 16   |

| Fig  |       | Turn-on transitions of 15 kV, 2 $\mu m$ and 5 $\mu m$ thick buffer layer, SiC IGBT at 10 kV, 8 A, 25°C with $R_{G(ON)}$ of 50 $\Omega$    | 17   |

| Fig. | 2.18: | Double pulse tester (14 kV peak) used for characterizing the IGBTs                                                                        | 18   |

| Fig. | 2.19: | Turn-on and turn-off switching voltage transitions with $dv/dt$ values at 11 kV, for the 2 $\mu$ m buffer layer thick 15 kV N-IGBT        | 19   |

| Fig. | 2.20: | The current turn-on spike of 15 kV, 20 A, 2 µm buffer layer IGBT at 10 kV, 8 A and 25°C                                                   | 20   |

| Fig. | 3.1:  | Turn-on and turn-off switching voltage transitions with dv/dt values at 11 kV, for the 2 $\mu$ m buffer layer thick 15 kV N-IGBT          | 22   |

| Fig. | 3.2:  | Circuit schematic of the isolation stage of the gate driver                                                                               | 24   |

| Fig. | 3.3:  | The cores evaluated for the isolation stage design of the HV gate driver                                                                  | . 24 |

| Fig. | 3.4:  | High isolation transformer designed using high voltage wire                                                                               | 26   |

| Fig. | 3.5:  | The coupling capacitance curve with respect to frequency up to 110 MHz                                                                    | . 26 |

| Fig. | 3.6:  | The high voltage gate driver prototype for the 15 kV SiC IGBT                                                                             | 28   |

| Fig. | 3.7:  | The half-bridge test circuit schematic used for 11 kV double-pulse validation of the gate driver                                          | 29   |

| Fig. | 3.8:  | The high-side IGBT (2 µm buffer layer) switching waveform at 11 kV validatin the gate driver                                              |      |

| Fig. | 3.9:  | The boost converter fed buck converter test circuit schematic used for 6 kV, 5 kHz validation of the gate driver                          | 31   |

| Fig. | 3.10: | Waveforms showing 6 kV, 5 kHz evaluation of the gate driver                                                                               | . 32 |

| Fig. | 3.11: | The buck-boost converter schematic used for 8 kV, 5 kHz validation of the gate driver                                                     | 32   |

| Fig. | 3.12: | Waveforms showing 8 kV, 5 kHz evaluation of the gate driver                                                                    | 33 |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. | 3.13: | Turn-on dv/dt during 8 kV, 5 kHz evaluation of the gate driver with $R_{G(ON)}\!=\!20~\Omega$                                  | 33 |

| Fig. | 3.14: | Turn-off dv/dt during 8 kV, 5 kHz evaluation of the gate driver with $R_{G(OFF)} \! = \! 10 \; \Omega$                         | 34 |

| Fig. |       | Experimental setup of buck-boost converter used for 8 kV, 5 kHz validation of the gate driver                                  | 35 |

| Fig. | 3.16: | Isolation power supply stage of the gate driver prototype with BNC connectors                                                  | 37 |

| Fig. | 3.17: | Waveforms of the common-mode voltage and its influence on the signals on the primary side of the isolation stage               | 38 |

| Fig. | 3.18: | Schematic of the isolation power supply of the gate driver showing primary side ground (GND) and output floating ground (FGND) | 38 |

| Fig. | 3.19: | The original isolation transformer (top) and the redesigned version for higher coupling capacitance (bottom)                   | 40 |

| Fig. | 3.20: | Waveforms of the common-mode voltage and its influence on the signals on the primary side of the redesigned isolation stage    | 40 |

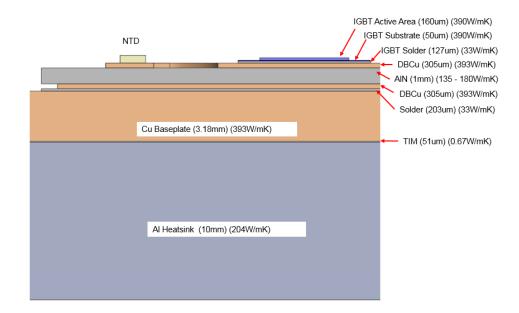

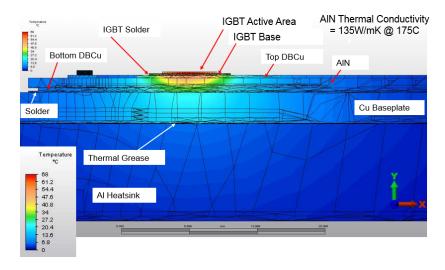

| Fig. | 4.1:  | The different layers in the IGBT module package contributing to the thermal Resistance                                         | 44 |

| Fig. | 4.2:  | Simulation result showing the temperature profile across the cross-section of the IGBT module for 125 W power dissipation      | 44 |

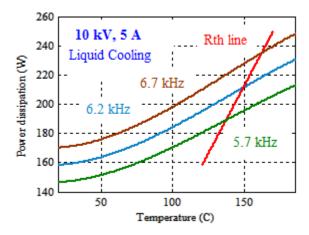

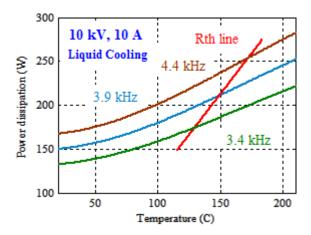

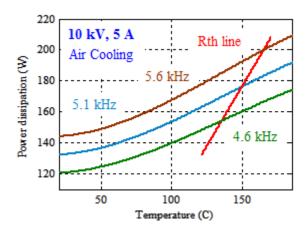

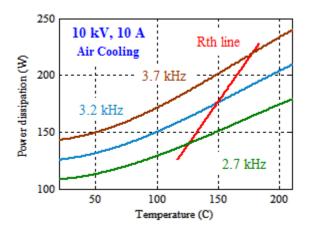

| Fig. | 4.3:  | Frequency limit curves at 10 kV, 5 A with liquid cooling                                                                       | 48 |

| Fig. | 4.4:  | Frequency limit curves at 10 kV, 10 A with liquid cooling                                                                      | 49 |

| Fig. | 4.5:  | Frequency limit curves at 10 kV, 5 A with air cooling                                                                          | 49 |

| Fig. | 4.6:  | Frequency limit curves at 10 kV, 10 A with air cooling                                                                         | 50 |

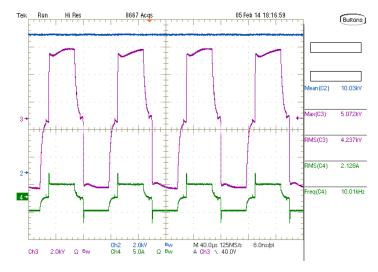

| Fig. | 4.7:  | The boost converter operation at 6.7 kHz, with 2 kV input and 10 kV output, at 6.4 kW                                          | 52 |

| Fig. 4.8:  | The turn-off transient during the 6.7 kHz operation of the boost converter at 10 kV, 6.4 kW output                              | 53 |

|------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.9:  | The turn-on transient during the 6.7 kHz operation of the boost converter at 10 kV, 6.4 kW output                               | 53 |

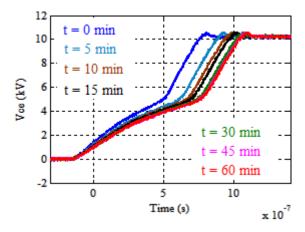

| Fig. 4.10: | The turn-off voltage curves during the 10 kV, 6.7 kHz boost converter demonstration                                             | 55 |

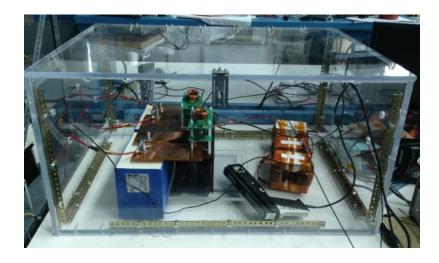

| Fig. 4.11: | The test setup of the 10 kV output dc-dc boost converter, demonstrating 15 kV SiC IGBT at 550 W/cm2 with air cooling            | 55 |

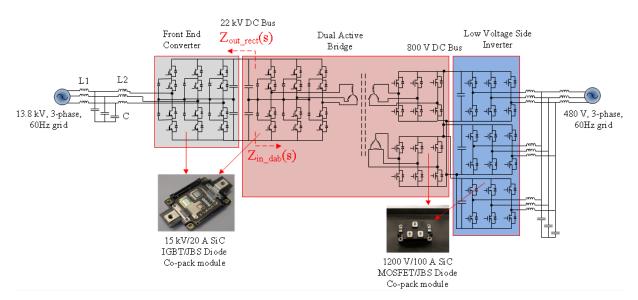

| Fig. 4.12  | The schematic of the transformerless intelligent power substation (TIPS) interfaced between 13.8 kV and 480 V three-phase grids | 56 |

| Fig. 4.13  | The bus-bar structure of the 3-level NPC pole                                                                                   | 58 |

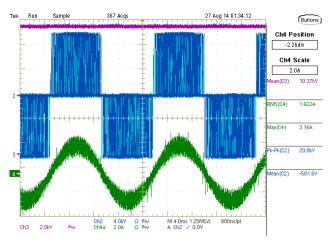

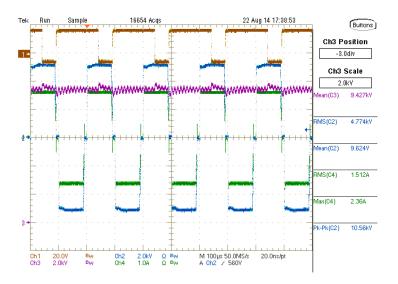

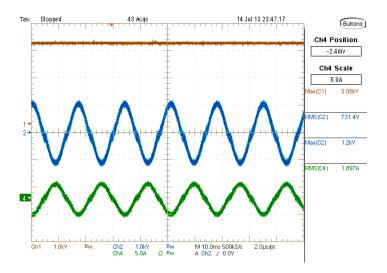

| Fig. 4.14: | The three-level converter pole waveforms at 10 kV, 10 kHz and 9 kW resistive load                                               | 58 |

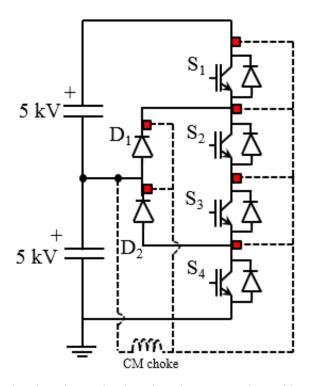

| Fig. 4.15  | The common currents from the heat sink to the dc-link midpoint with direct shorting                                             | 59 |

| Fig. 4.16  | The common currents from the heat sink to the dc-link midpoint with 3 mH choke                                                  | 59 |

| Fig. 4.17: | The 3-level pole schematic showing the connection of base plate to the dc-bus midpoint through a common-mode choke              | 60 |

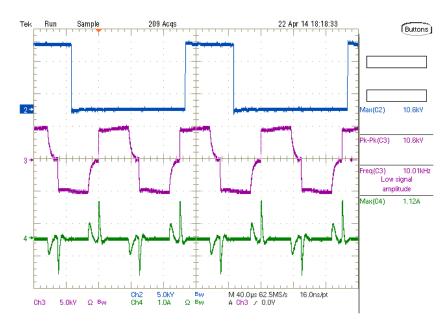

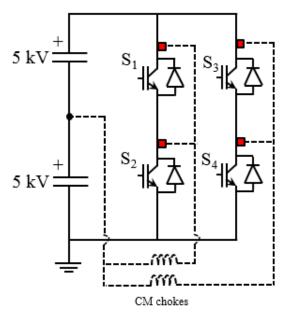

| Fig. 4.18  | The schematic of H-bridge showing the connection of each heatsink to the midpoint using separate common-mode chokes             | 62 |

| Fig. 4.19: | The waveforms of the H-Bridge with 10 kV dc input at 5 kHz and 6 kW operation                                                   | 63 |

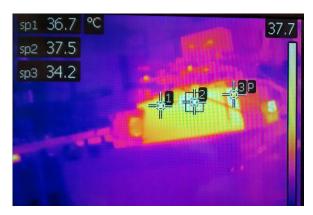

| Fig. 4.20: | The thermal image of the converter system at the end of 15 minute operation                                                     | 63 |

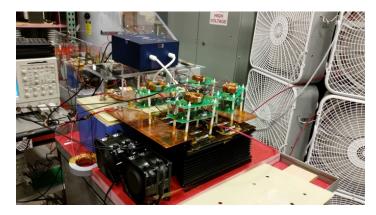

| Fig. 4.21: | The lab experimental test setup of the H-Bridge converter                                                                       | 64 |

| Fig. 4.22  | The pictorial view of the two-chip 15 kV IGBT co-pack                                                                           | 65 |

| Fig. 4.23  | The turn-on energy loss and turn-off energy comparison of the single-chip and two-chip 15 kV IGBT modules at 5 kV               | 66 |

| Fig. 4.24: | The turn-on and turn-off energy loss comparison at 5 kV and 5 A at different temperature and gate resistances, for single-chip 15 kV IGBT module          | 6 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

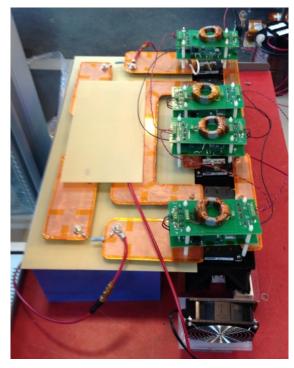

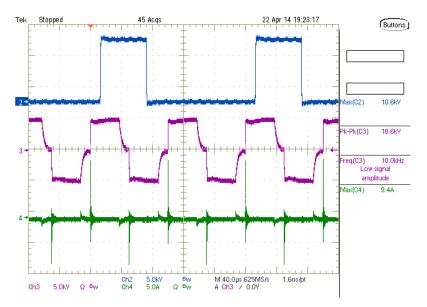

| Fig. 4.25: | The 3-level pole waveforms with 10 kV dc-input, sine-PWM modulation for rectifier stage at 5 kHz switching and 7.2 kW                                     | 8 |

| Fig. 4.26: | The 3-level pole operation with 10 kV dc-input, square-PWM modulation for DAB stage at 5 kHz and 7.2 kW                                                   | 8 |

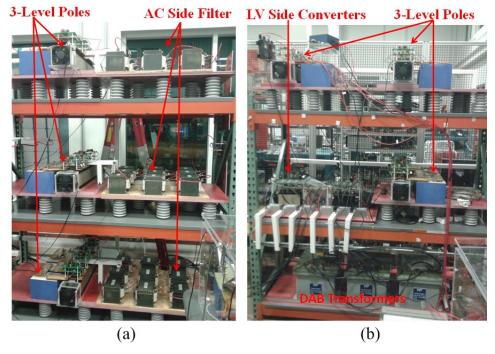

| Fig. 4.27: | The laboratory test setup of the TIPS system. (a) Front-end Converter (rectifier) (b) dc-dc dual active bridge (DAB) with high frequency transformers     | 9 |

| _          | Turn-off transition of 15 kV, 2 $\mu m$ IGBT at 11 kV, 10 A, 25°C with $R_{G(OFF)}$ of 10 $\Omega$                                                        | 2 |

| _          | Representation of carrier concentration in the drift and buffer layer (B/L) of the 15 kV SiC IGBT under high level injection conditions                   | 3 |

|            | A depiction of electric field profile as the drift and buffer layers are depleted during the turn-off process of the SiC IGBT                             | 4 |

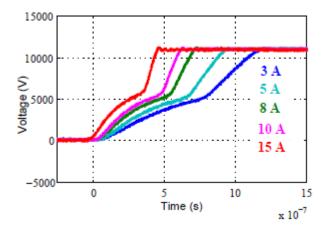

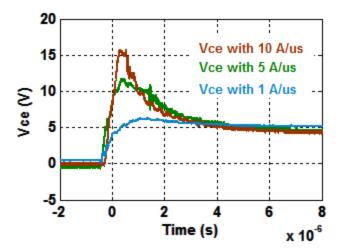

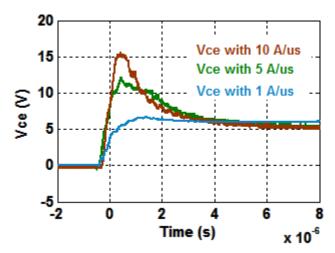

| _          | Turn-off voltage transitions of 15 kV, 2 $\mu m$ thick buffer layer, SiC IGBT at 11 kV, 25°C with $R_{G(OFF)}$ of 10 $\Omega$ , with varying load current | 5 |

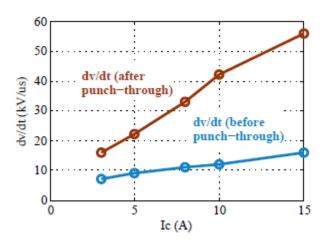

| Fig. 5.5:  | Turn-off dv/dt values of 15 kV, 2 $\mu m$ thick buffer layer, SiC IGBT at 11 kV, 25°C with $R_{G(OFF)}$ of 10 $\Omega$ , with varying load current        | 5 |

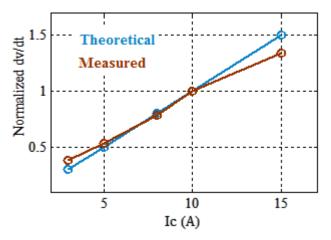

| Fig 5.6:   | The measured and calculated normalized dv/dt values after punch-through at 11 kV, 10 A, 25°C                                                              | 6 |

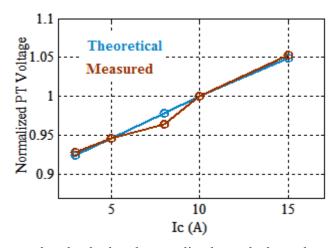

| Fig. 5.7:  | The measured and calculated normalized punch-through transition voltage values with reference to the punch-through voltage at 11 kV, 10 A, 25°C7          | 7 |

|            | Turn-off transitions of 15 kV, 2 $\mu m$ and 5 $\mu m$ thick buffer layer, SiC IGBT at 10 kV, 10 A, 25°C with R <sub>G(OFF)</sub> of 10 $\Omega$          | 8 |

| Fig. 5.9:  | Representation of carrier profile in the 2 µm and 5 µm buffer layer thick SiC IGBTs                                                                       | 9 |

| _          | Turn-on transitions of 15 kV, 2 $\mu m$ and 5 $\mu m$ thick buffer layer, SiC IGBT at 10 kV, 8 A, 25°C with $R_{G(ON)}$ of 50 $\Omega$                    | 0 |

| Fig. | 5.11: | Turn-on transitions of 15 kV, 2 $\mu$ m thick buffer layer, SiC IGBT at 10 kV, 8 A, 25°C with $R_{G(ON)}$ of 50 $\Omega$                                                        | .80 |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. | 5.12: | Turn-on and turn-off dv/dt variation with temperature of 5 $\mu$ m thick buffer layer SiC IGBT at 8 kV, 5 A with $R_{G(ON)}$ of 50 $\Omega$ and $R_{G(OFF)}$ of 10 $\Omega$     | .81 |

| Fig. | 5.13: | Representation of carrier profile in the 15 SiC IGBTs with respect to temperature                                                                                               | .82 |

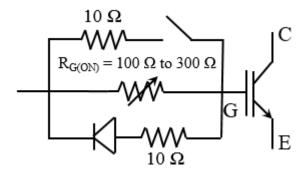

| Fig. | 5.14: | The gate resistance configuration for the non-active gating of the 15 kV IGBT                                                                                                   | 84  |

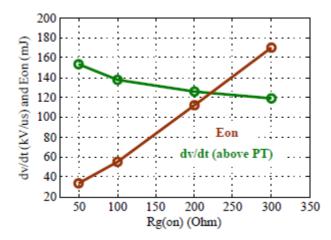

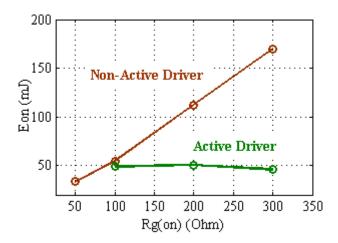

| Fig. | 5.15: | The turn-on dv/dt and the energy loss with increase in $R_{G(ON)}$ from 50 $\Omega$ to 300 $\Omega$ , at 11 kV, 8 A and 25°C of the 2 $\mu$ m, 15 kV IGBT                       | .85 |

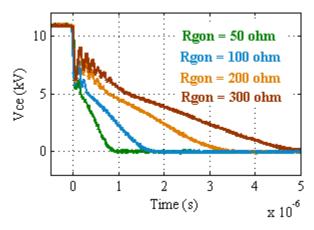

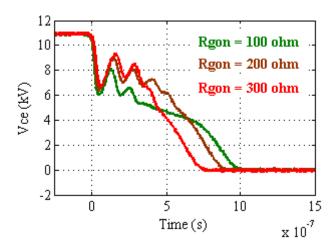

| Fig. | 5.16: | The voltage transitions with increase in $R_{G(ON)}$ from 50 $\Omega$ to 300 $\Omega$ , at 11 kV, 8 A and 25°C of the 2 $\mu m$ , 15 kV IGBT using non-active gate driver       | .85 |

| Fig. | 5.17: | The gate resistance configuration used for the active gating of the 15 kV SiC IGBT                                                                                              | .86 |

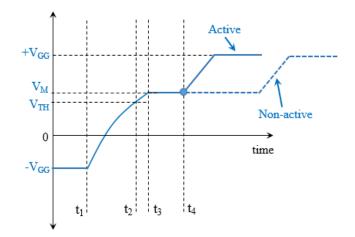

| Fig. | 5.18: | The representation of two-stage active vs. non-active gate waveforms showing different instants during turn-on transition                                                       | .87 |

| Fig. | 5.19: | The gate voltage of the IGBT with $R_{G(ON)}$ of 200 $\Omega$ , at zero collector bias for both non-active and active gate driving cases                                        | .87 |

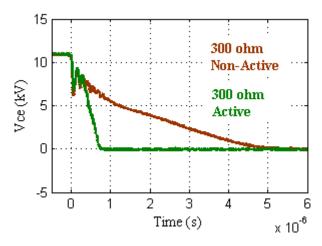

| Fig. | 5.20: | The variation of the energy loss with $R_{G(ON)}$ from 50 $\Omega$ to 300 $\Omega$ , at 11 kV, 8 A and 25°C of the 2 $\mu m$ , 15 kV SiC IGBT with non-active and active gating | .88 |

| Fig. | 5.21: | The voltage transitions with increase in $R_{G(ON)}$ from 100 $\Omega$ to 300 $\Omega$ , at 11 kV, 8 A and 25 °C of the 2 $\mu m$ , 15 kV SiC IGBT using active gate driver     | .88 |

| Fig. | 5.22: | The IGBT turn-on voltage transitions at 11 kV, 8 A and 25°C of the 2 $\mu$ m, 15 kV IGBT with $R_{G(ON)}$ of 300 $\Omega$ under non-active and active gating                    | .89 |

| Fig. | 5.23: | The IGBT turn-on voltage transitions at 11 kV, 8 A and 25°C of the 2 $\mu$ m, 15 kV IGBT with $R_{G(ON)}$ of 100 $\Omega$ under non-active and active gating                    | .90 |

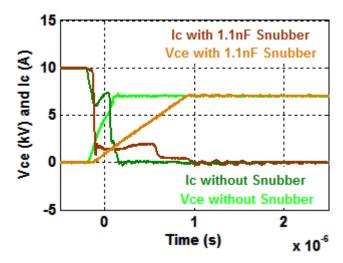

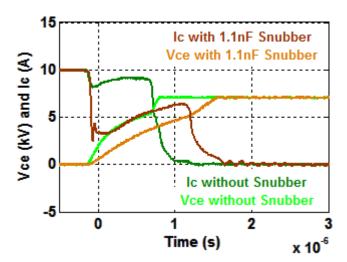

| Fig. | 6.1:  | Turn-on voltage spike of 12 kV, 2 µm buffer layer SiC IGBT under different di/dt conditions at 150°C                                                                            | .93 |

| Fig. | 6.2:  | Turn-on voltage spike of 12 kV, 5 µm buffer layer SiC IGBT under different di/dt conditions at 150°C                                                                            | .94 |

| Fig. 6.3: | Turn-on voltage spike of 12 kV, 5 $\mu m$ buffer layer SiC IGBT under di/dt of 5 A/ $\mu s$ at 25°C and 150°C                                          | 94   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 6.4: | Turn-off transitions of 12 kV, 2 µm buffer layer SiC IGBT at 25°C and 150°C without an external snubber capacitor                                      | 95   |

| Fig. 6.5: | Turn-off transitions of 12 kV, 2 µm buffer layer SiC IGBT at 25°C with and without the 1.1 nF external snubber capacitor                               | 96   |

| Fig. 6.6: | Turn-off transitions of 12 kV, 2 µm buffer layer SiC IGBT at 150°C with and without the 1.1 nF external snubber capacitor                              | 96   |

| Fig. 6.7: | Turn-off transitions of 12 kV, 5 µm buffer layer SiC IGBT at 25°C and 150°C without an external snubber capacitor                                      | 97   |

| Fig. 6.8: | Turn-off transitions of 12 kV, 5 µm buffer layer SiC IGBT at 25°C with and without the 1.1 nF external snubber capacitor                               | 97   |

| Fig. 6.9: | Turn-off transitions of 12 kV, 5 µm buffer layer SiC IGBT at 150°C with and without the 1.1 nF external snubber capacitor                              | 98   |

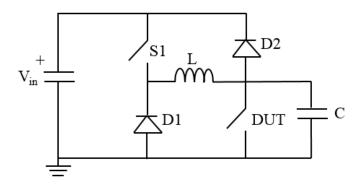

| Fig. 6.10 | : Test circuit used for ZVS characterization of the IGBTs                                                                                              | 98   |

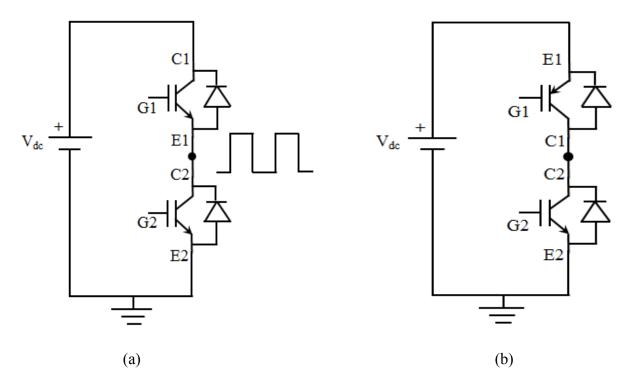

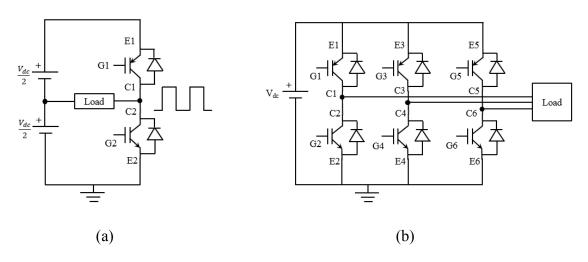

| Fig. 7.1: | Schematic of (a) Inverter phase-leg with N-type devices; (b) Phase-leg of complementary inverter with P-type device on top and N-type device on bottom | .103 |

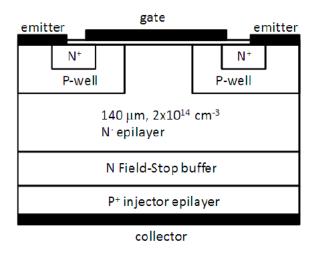

| Fig. 7.2: | Cross-sectional view of the 15 kV P-IGBT.                                                                                                              | .104 |

| Fig. 7.3: | Turn-off transition of the 15 kV, 5 A, P-IGBT with clamped inductive load at 6 kV, 5 A with $R_{G(OFF)}=10~\Omega$                                     | .105 |

| Fig 7.4:  | Turn-on transition of the 15 kV, 5 A, P-IGBT with clamped inductive load at 6 kV and 5 A with $R_{G(ON)}$ = 200 $\Omega$ .                             | .105 |

| Fig. 7.5: | Cross-sectional view of the 15 kV N-IGBT                                                                                                               | 106  |

| Fig. 7.6: | Turn-off transition of the 15 kV, 5 A, N-IGBT under clamped inductive load test at 6 kV and 5 A with $R_{G(OFF)}$ = 10 $\Omega$ .                      | .107 |

| Fig. 7.7: | Turn-on transition of the 15 kV, 5 A, N-IGBT under clamped inductive load test at 6 kV and 5 A with $R_{G(ON)}$ = 200 $\Omega$                         | .107 |

| Fig. 7.8: | Representation of stored charge in P-IGBT and N-IGBT                                                                                                   | .110 |

| Fig. | 7.9:  | Schematic of (a) half-bridge complementary inverter; (b) three-phase complementary inverter      | 111 |

|------|-------|--------------------------------------------------------------------------------------------------|-----|

| Fig. | 7.10: | Experimental waveforms of the half-bridge complementary inverter at 5 kHz switching frequency    | 111 |

| Fig. | 7.11: | Experimental waveforms of the half-bridge complementary inverter with 10 kHz switching frequency | 112 |

| Fig. | 7.12: | Experimental waveforms of the three phase complementary inverter at 5 kHz switching frequency    | 112 |

| Fig. | 7.13: | The prototype of the complementary half-bridge inverter with 15 kV SiC IGBTs                     | 113 |

| Fig. | 7.14: | The prototype of the complementary three phase inverter with 15 kV SiC IGBTs                     | 113 |

# Chapter 1

# Introduction

#### 1.1 Background

The silicon (Si) MOSFETs and IGBTs are most widely used power semiconductor devices today. MOSFETs are suitable for high switching frequency but are typically limited to a kilovolt in practical applications due to increase in on-resistance resulting from the unipolar physics. On the other hand, IGBTs are attractive over a wide range of voltages, beginning from about 600 V to 6.5 kV (device blocking voltage) owing to their bipolar physics of operation with simple MOS gate control. The development of further higher voltage Si IGBTs is limited by increased energy losses resulting from the fundamental material properties of Si.

At this juncture, 4H-SiC has been found to be a viable alternative due to its much wider bandgap. The several fold increase in critical electric field in comparison to Si makes it feasible to build high voltage unipolar devices with extremely low resistance as predicted by Baliga's figure of merit [1]. The better thermal conductivity properties of SiC is another factor of considerable importance which is critical in heat removal process [2]-[3]. The high temperature capability of SiC, due to its wider band-gap, is another attractive feature.

These unique advantages of SiC led to development of MOSFETs beyond 10 kV [4]-[5]. The 10 kV SiC MOSFETs have been demonstrated on a single-phase 1 MVA soft-switched Solid State Power Substation (SSPS) by GE in the year 2010 – 2011 [5]. The 13 kV SiC MOSFETs have been demonstrated on a 20 kVA single-phase Solid State Transformer (SST) by FREEDM Center at North Carolina State University [6]-[7].

However, similar to the case of silicon, as the voltage is scaled-up, IGBT is more efficient due to its bipolar physics with MOS gate structure. Therefore, significant research effort has been spent in the recent years to develop high voltage 4H-SiC IGBTs. Due to difficulty in producing low resistivity P+ substrate, the initial SiC IGBTs have been developed with P-channel (using

N+ substrate) [8]. However, with advances in SiC technology, low resistivity P+ substrates have been developed leading to the development of SiC N-IGBTs [9]. The characteristics of 12.5 kV N-IGBTs and 15 kV P-IGBT have already been reported up to switching voltage of 8 kV [10]. However, there has been no literature on converter design and demonstration using these ultrahigh voltage SiC IGBTs.

The objective of this thesis is to understand the state-of-the-art 15 kV SiC N-IGBTs with emphasis on the design considerations for optimal and reliable application to high power conversion. As SiC N-IGBTs over 20 kV are being developed [11], understanding behavior of the 15 kV devices is crucial in paving way for scaling up the design techniques for their application in power conversion systems.

#### 1.2 Outline of this Dissertation

This thesis is organized as follows.

Chapter-1 provides the prior art of the research on high voltage SiC power semiconductor devices and their demonstration, followed by motivation of the work presented in this thesis.

Chapter-2 begins with the switching characterization of the 15 kV SiC N-IGBTs up to 10 kV and  $175^{\circ}$ C under inductive, partly inductive and resistive loads. A comparison of 2  $\mu$ m and 5  $\mu$ m field-stop buffer layer N-IGBTs is provided. This is followed by a short discussion on understanding the design considerations of power conversion system using these devices.

Chapter-3 presents the gate driver design and its evaluation as per the requirements determined in switching tests presented in Chapter-2. Different test circuits are built to validate the gate driver in continuous switching tests and the robustness evaluation results of the gate driver are provided.

Chapter-4 is devoted to demonstrating the 5 µm buffer layer 15 SiC N-IGBTs. The SiC IGBT is first demonstrated on 10 kV boost converter heat-run tests. This was followed by three-level

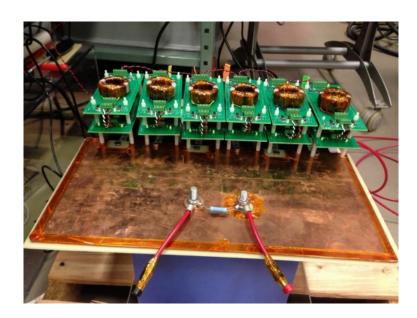

NPC converter demonstration with 10 kV dc-input in inverter mode with sine-PWM and square-PWM modulation. The performance of multi-chip IGBT module is also provided.

Chapter-5 presents analysis of the dv/dt generated by the SiC IGBTs, with varying collector current, temperature and buffer layer thickness, based on the experimental evaluation. The latter part of the chapter is devoted to development of two-stage active gate driver to minimize turn-on dv/dt without increasing energy loss.

Chapter 6 is continuation of the investigation on optimal performance of the SiC IGBTs. The behavior of the IGBTs under zero voltage switching conditions is evaluated under different conditions. This is followed by understanding its impact on soft-switched converter applications.

Chapter 7 provides investigation on the 15 kV SiC P-IGBT and N-IGBT based complementary inverter to have zero dv/dt stress on the gate drivers.

Chapter 8 summarizes the contributions of the work and future research direction on this subject.

# Chapter 2

# Hard Switching Characterization of 15 kV SiC N-IGBTs

#### 2.1 Introduction

In [10], switching characteristics of 12.5 kV SiC N-IGBTs and 15 kV SiC P-IGBTs have been reported up to 8 kV. The 15 kV SiC N-IGBTs are the state-of-the-art devices whose switching characteristics have never been reported previously. Moreover, it is important to experimentally validate the switching behavior of the 15 kV SiC N-IGBTs at least up to 10 kV considering their operation in a power converter system due to voltage surges and overhead incorporated for the protection circuitry. Also, the turn-on switching characteristics of the SiC IGBTs and their influence on power converter design have never been reported. Therefore, a high voltage switching test setup has been built with nominal rating of 12 kV (with peak voltage of 14 kV) to characterize the 15 kV SiC IGBTs for both turn-on and turn-off at different temperature. The 15 kV SiC N-IGBTs are designed and built by Cree, and the packaging and static (forward conduction and leakage) characteristics are provided by Powerex.

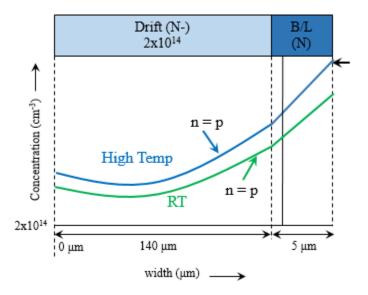

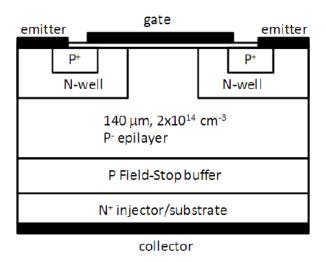

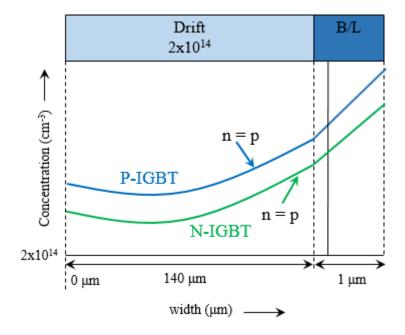

#### 2.2 The 15 kV SiC N-IGBT

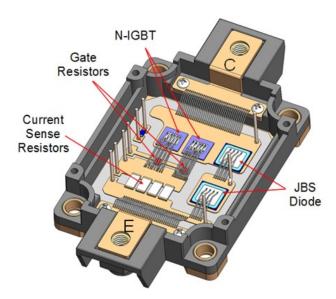

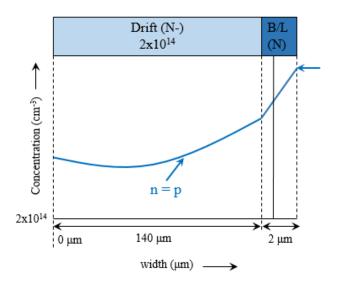

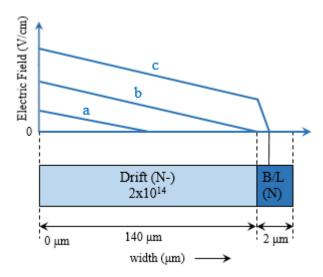

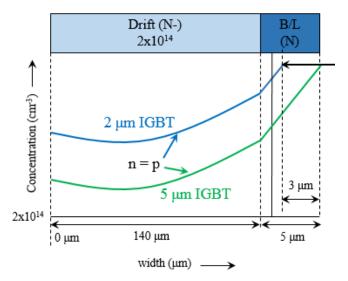

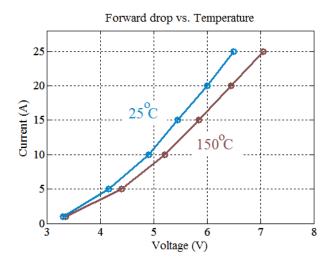

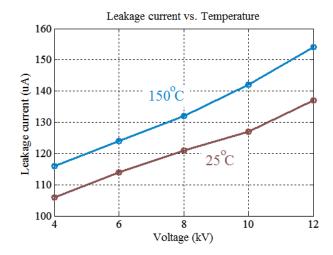

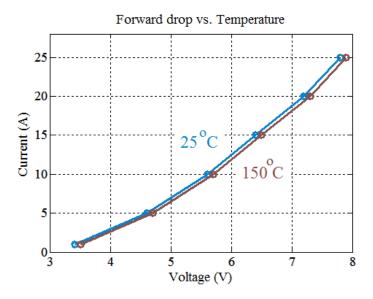

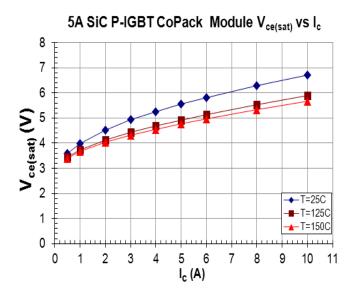

The simplified cross-sectional view of the 15 kV SiC N-IGBT is shown in Fig. 2.1. The drift layer is 140 µm thick with doping concentration of  $2x10^{14}$  cm<sup>-3</sup>. The IGBT used for the characterization has a buffer layer thickness of 5 µm, and its chip area is 0.84cmx0.84cm, with an active area of 0.32 cm<sup>2</sup>. Fig 2.2 shows the co-pack module with the 15 kV SiC IGBT with 20 kV (2x10 kV) SiC JBS diodes. The current-sense resistors and the thermistor integrated in the module for over current and temperature protection are seen in the figure. The forward

conduction and leakage characteristics of the IGBT are provided by powerex, and are shown in Appendix.

Fig. 2.1: Simplified cross-sectional view of 15 kV SiC N-IGBT

Fig. 2.2: 15 kV SiC N-IGBT co-pack module

#### 2.3 Hard-switching Characteristics

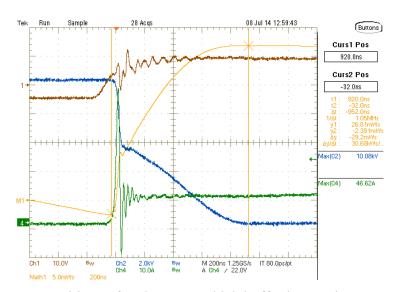

In this section, fully hard-switching characteristics of the 15 kV, 5  $\mu$ m buffer layer IGBT are presented for purely inductive, partly inductive and fully resistive load conditions up to 10 kV. The turn-on gate resistance,  $R_{G(ON)}$ , used is 20  $\Omega$ , and the turn-off gate resistance,  $R_{G(OFF)}$ , used is 10  $\Omega$ . The IGBT voltage is measured using Tektronix 20 kV, 75 MHz single-ended probe, and the IGBT current is measured using a pearson coil of 20 MHz bandwidth. The 500 MHz oscilloscope is set to 150 MHz for the voltage measurement and 20 MHz for the current measurement.

#### 2.3.1 Clamped-Inductive Load Switching Conditions

The clamped inductive (or fully hard-switched) characteristics are most widely provided data for power semiconductor devices to cover majority of applications. The circuit schematic of the double-pulse test circuit is shown in Fig. 2.3. The freewheeling diode used in the switching tests is 20 kV SiC JBS diode module (2x10 kV, 10 A diodes in series). The load is a single-layer, 8 mH inductor (two 4 mH inductors in series) with saturation current of 30 A (shown in Fig. 2.4) and with ultralow inter-winding capacitance (estimated to be < 10 pF). Experiments have been performed at 10 kV with varying current and temperature.

Fig. 2.3. The double-pulse test circuit schematic with different parasitic components

Fig. 2.4: The high voltage, low capacitance, HV load inductor (4 mH, 30 A). Two of them have been used in series for the switching characterization tests.

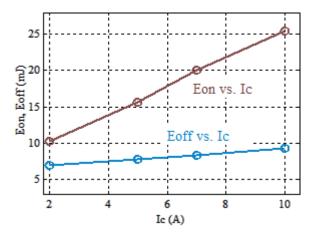

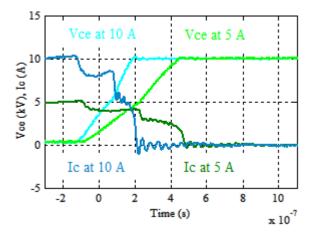

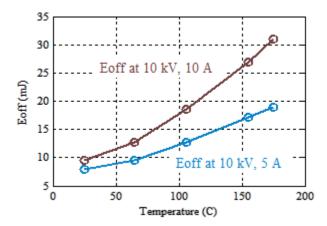

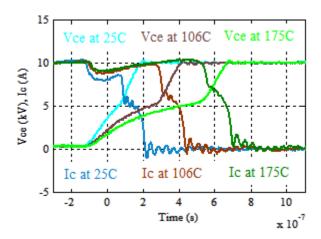

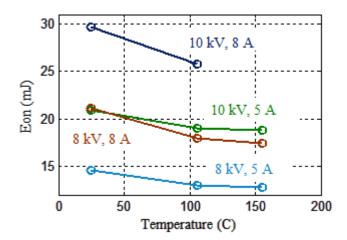

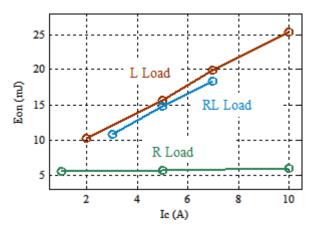

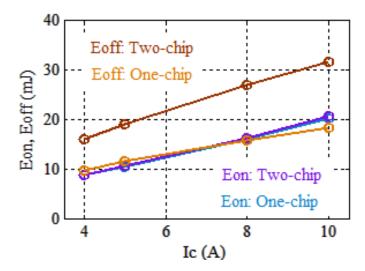

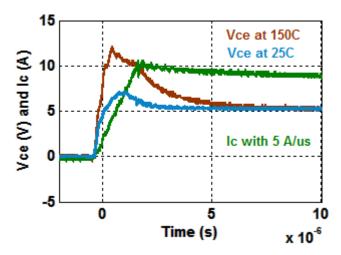

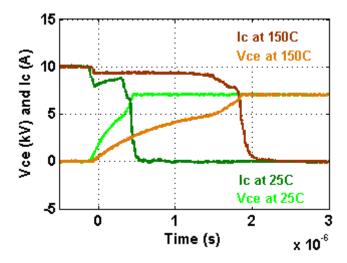

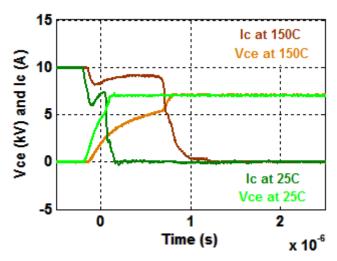

Fig. 2.5 shows turn-on switching loss (EoN) and turn-off switching loss (EoFF) at 25°C, at 10 kV, 2 A to 10 A. Unlike the turn-on loss, the turn-off loss is weakly dependent on the current. Fig. 2.6 shows the turn-off transitions at 10 kV, 5 A, and 10 A at 25°C. The duration of the 10 A transition is about 60 % of that of the 5 A transition, resulting in very slight variation of energy loss from 5 A to 10 A. The temperature dependency of the turn-off loss is shown in Fig. 2.7. The energy loss is increased to a factor of three from 25°C to 175°C, due to increased injection at higher temperature resulting in significantly larger amounts of charge in the drift region. As shown in Fig. 2.8, the larger amount of charge to be removed at higher temperature is slowing down the voltage rise (before punch through) which in consequence is resulting in higher energy loss. The switching energy losses reported in the entire thesis are calculated online using the oscilloscope math function, ∫ v. i. dt on IGBT voltage and current.

Fig. 2.5: Turn-on and turn-off energy loss values with current variation at 10 kV and 25°C, under clamped inductive load.

Fig. 2.6: Turn-off switching transitions at 10 kV, 25°C, 5 A and 10 A, under clamped inductive load conditions.

Fig. 2.7: Turn-off switching loss variation with temperature at 5 A and 10 A at 10 kV, under clamped inductive load conditions.

Fig. 2.8: Turn-off switching transitions with temperature at 10 kV and 10 A, under clamped inductive load conditions.

The turn-off loss at different temperature values is summarized in Table 2.1. The hot plate was allowed to reach steady state for an hour before characterizing the switching transient at a particular temperature. The difference in reading between the hot plate display and the thermistor mounted in the IGBT module (shown in Fig. 2.2) are provided in the table. The thermistor (rated for 150°C) temperature values are taken as reference for the entire study. The turn-on energy loss is not as strongly dependent on temperature as shown in Fig. 2.9. The

$R_{G(ON)}$  used is 33  $\Omega$  for the temperature dependency turn-on loss characterization, unlike the rest of the experiments which were conducted with  $R_{G(ON)}$  of 20  $\Omega$ . The use of 20  $\Omega$   $R_{G(ON)}$  has damaged the hot-plate used for the characterization, most probably due to the EMI. Therefore, the turn-on loss behavior at high temperature is evaluated with higher gate resistance of 33  $\Omega$ . Based on the results shown in Fig. 2.9 and Table 2.2, the turn-on energy loss is not drastically varying with temperature, unlike the turn-off energy loss.

Table 2.1: Inductive turn-off energy loss values at 10 kV, 5 A and 10 A.

| Hot-plate<br>Setting | Thermistor<br>Reading | E <sub>OFF</sub> at 10 kV, 5 A | E <sub>OFF</sub> at 10 kV, 10 A |

|----------------------|-----------------------|--------------------------------|---------------------------------|

| 25°C                 | 26°C<br>(Measured)    | 8.0 mJ                         | 9.6 mJ                          |

| 75°C                 | 65°C<br>(Measured)    | 9.6 mJ                         | 12.7 mJ                         |

| 125°C                | 106°C<br>(Measured)   | 12.7 mJ                        | 18.6 mJ                         |

| 175°C                | 155°C<br>(Measured)   | 17.2 mJ                        | 27.0 mJ                         |

| 195°C                | 175°C<br>(Estimated)  | 19.0 mJ                        | 31.0 mJ                         |

Fig. 2.9: The turn-on energy loss variation of 15 kV N-IGBT with temperature with  $R_{G(ON)} = 33 \Omega$ .

Table 2.2: Turn-on energy loss variation of 15 kV N-IGBT with temperature

| Voltage and<br>Current | E <sub>ON</sub> at 25°C | E <sub>ON</sub> at<br>106°C | E <sub>ON</sub> at<br>155°C |

|------------------------|-------------------------|-----------------------------|-----------------------------|

| 8 kV, 5 A              | 14.6 mJ                 | 13.0 mJ                     | 12.8 mJ                     |

| 8 kV, 8 A              | 21.1 mJ                 | 18.0 mJ                     | 17.4 mJ                     |

| 10 kV, 5 A             | 20.9 mJ                 | 19.0 mJ                     | 18.8 mJ                     |

| 10 kV, 8 A             | 29.7 mJ                 | 25.8 mJ                     | N/A                         |

#### 2.3.2 Partly Inductive Load Switching Conditions

The majority of the power converter applications fall into the fully hard-switching category due to the high L/R time constants of the RL loads. The hard-switching characteristics provided in the previous subsection address this category. For very high L/R loads, as the time constant is very large in comparison to the switching duration, the behavior corresponds to the fully inductive load conditions. However, some applications like dual active bridge converters with high frequency transformers have low L/R time constant loads, where the assumption of fully

inductive load is not valid particularly under light load conditions. To understand the behavior of the IGBT under those conditions, a 1 k $\Omega$  resistance in series with the 8 mH inductor (8µs time constant) is used as the load in this subsection.

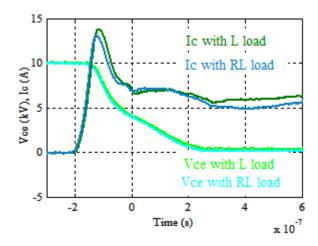

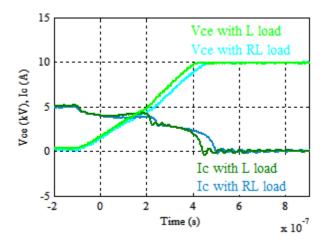

Based on the 25°C turn-on and turn-off transitions shown in Fig. 2.10 and Fig. 2.11 respectively, at 10 kV and 5 A, the RL load is behaving almost as the purely inductive load at 25°C, except for slightly lower peak during turn-on and slower transition during turn-off. The reason for this behavior is the longer time constant of the RL load in comparison to the switching transition duration. The slower turn-off transition is due to the inductive energy dissipation during the switching transition causing reduced load current. It must be noted that the effects of RL nature of the load would have been dominant during the turn-off transition if the measurements were made at higher temperature due to longer switching transition duration.

Fig. 2.10: Comparison of turn-on transitions with L and RL loads at 10 kV and 5 A, at 25°C.

Fig. 2.11: Comparison of turn-off transitions with L and RL loads at 10 kV and 5 A, at 25°C.

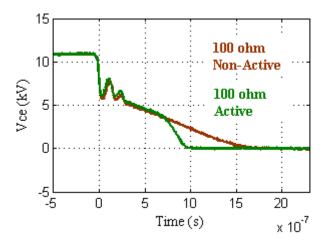

#### 2.3.3 Resistive Load Switching Conditions

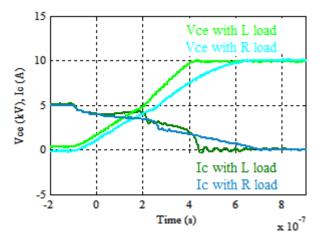

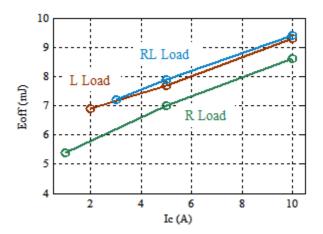

This switching characterization is done with 2 kΩ wire-wound resistor (with stray inductance of 0.3 mH) at 10 kV and 5 A. The tests at other load currents are conducted by appropriately scaling the load resistance values for the desired current value. Unlike the case for RL load, the R load presents significantly different turn-on and turn-off characteristics in comparison to the purely L load characteristics. The current spike is significantly reduced due to zero current turn-on, and also probably due to absence of load capacitance. The resistive turn-on and turn-off transitions at 10 kV, 5 A and 25°C are compared with corresponding inductive characteristics in Fig. 2.12 and Fig. 2.13 respectively. The turn-on and turn-off energy loss comparison with the different loads is provided in Fig. 2.14 and Fig. 2.15 respectively. The L and RL loads have almost same amount of energy loss during turn-on and turn-off transitions. The zero current turn-on is resulting in same energy loss at different currents with the R load. The energy dissipation (load current reduction in the R load) during turn-off transition reduces IGBT current and consequently the turn-off loss, in comparison to that with L or RL load.

Fig. 2.12: Comparison of turn-on transitions with L and R loads at 10 kV and 5 A, at 25°C.

The resistive load does not find wide real-time application. However, the characteristics are provided to show behavior of the IGBT under all possible loads. The heating applications where pure R load conditions are seen, are realized by using a series capacitor (for resonance) to cancel the impedance offered by the stray inductance of the coils.

Fig. 2.13: Comparison of turn-off transitions with L and R loads at 10 kV and 5 A, at 25°C.

Fig. 2.14: Comparison of turn-on energy loss with L, RL and R loads at 10 kV and 25°C.

Fig. 2.15: Comparison of turn-off energy loss with L, RL and R loads at 10 kV and 25°C.

# 2.4 Comparison of 15 kV 5 $\mu m$ and 2 $\mu m$ buffer layer N-IGBTs

The 15 kV SiC N-IGBT characteristics reported in the earlier section has 5 µm thick field-stop buffer layer (refer cross-sectional view of the IGBT shown in Fig. 2.1). This section is devoted to understanding the characteristics of the SiC IGBT, from an application perspective, if the field-stop buffer layer thickness is varied.

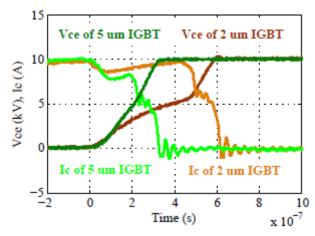

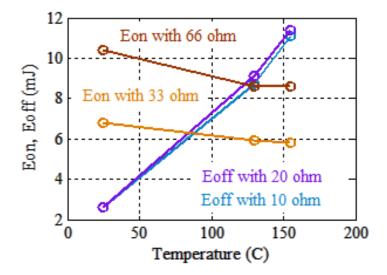

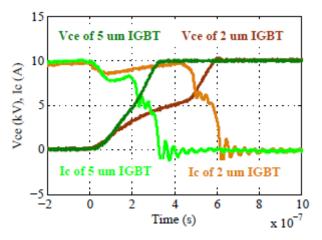

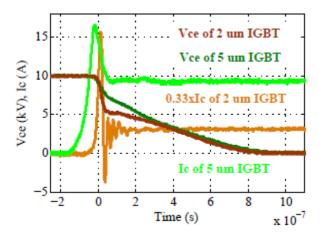

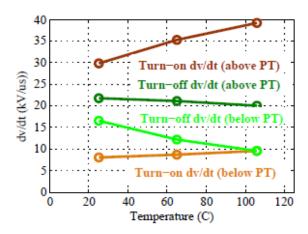

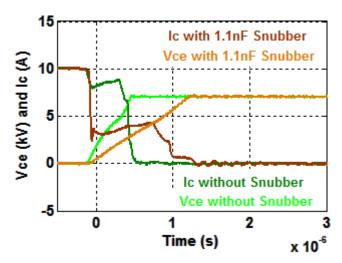

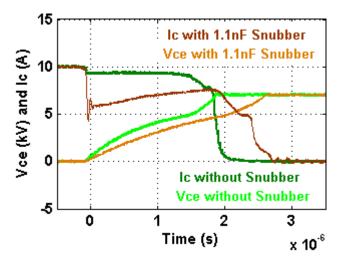

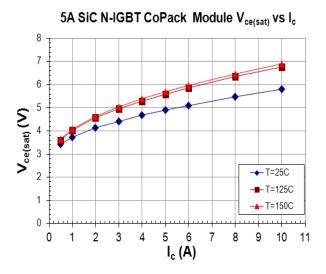

The forward conduction characteristics of both the 15 kV SiC IGBT are provided in Appendix. The reduction in buffer layer thickness from 5  $\mu m$  to 2  $\mu m$  has reduced the conduction drop from 7.2 V to 6.0 V at 20 A. Both the IGBTs have been designed with same drift layer parameters and same buffer layer doping, except for its thickness. Fig. 2.16 shows turn-off transition of 2  $\mu m$  and 5  $\mu m$  buffer layer IGBTs at 10 kV and 10 A. The turn-off transition of the 5  $\mu m$  buffer layer IGBT is much faster than that of the 2  $\mu m$  buffer layer IGBT, due to reduced injection, explained in Chapter-5.

Fig. 2.16: Turn-off transitions of 15 kV, 2  $\mu m$  and 5  $\mu m$  thick buffer layer, SiC IGBT at 10 kV, 10 A, 25°C with  $R_{G(OFF)}$  of 10  $\Omega$ .

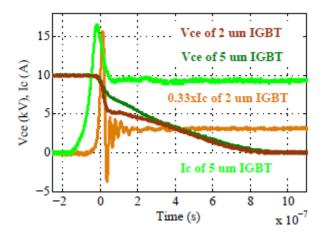

The turn-on transitions of both the IGBTs at 10 kV, 8 A are shown in Fig. 2.17. The 2  $\mu$ m IGBT has significantly larger dv/dt above the punch-through voltage resulting in a large current spike due to discharge of the capacitance of the free-wheeling diode of the clamped inductive test circuit. It should be noted that the current waveform of the 2  $\mu$ m buffer layer IGBT is scaled to 0.33x in Fig. 2.17. The ringing in the gate voltage is due to the high di/dt probe pickup resulting from the discharge of the capacitance of the free-wheeling diode. Table 2.3 summarizes dv/dt values of both the devices at 25°C with  $R_{G(ON)} = 50 \Omega$  and  $R_{G(OFF)} = 10 \Omega$ . Table 2.4 summarizes energy loss values of both the IGBTs. Based on the data shown in these two tables, the thicker buffer layer IGBT has significantly lower turn-off loss and turn-on dv/dt

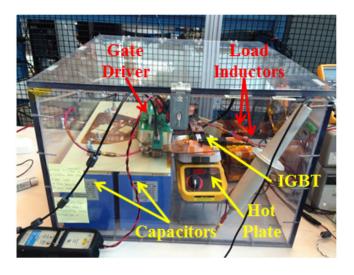

(over punch-through voltage). However, the conduction drop is moderately increased due to the thicker buffer layer. Thus, the 5  $\mu$ m devices are more suitable for high frequency, high voltage power conversion. Fig 2.18 shows the high voltage double-pulse switching test setup used for characterizing the SiC IGBTs.

Fig 2.17: Turn-on transitions of 15 kV, 2  $\mu m$  and 5  $\mu m$  thick buffer layer, SiC IGBT at 10 kV, 8 A, 25°C with  $R_{G(ON)}$  of 50  $\Omega$  (The 2  $\mu m$  IGBT current is scaled down to 0.33x to accommodate the current spike).

Table 2.3: dv/dt of 2 µm and 5 µm IGBTs at 10 kV, 8 A (turn-on) and 10 A (turn-off)

| Parameter                  | 2 μm IGBT<br>(kV/μs) | 5 μm IGBT (kV/μs) |

|----------------------------|----------------------|-------------------|

| Turn-on dv/dt (above PT)   | 135                  | 39                |

| Turn-on dv/dt (under PT)   | 7.3                  | 9.0               |

| Turn-off dv/dt (before PT) | 12                   | 30                |

| Turn-off dv/dt (after PT)  | 39                   | 47                |

Table 2.4: Energy loss values of 15 kV, 2  $\mu m$  and 5  $\mu m$  SiC IGBTs

| Parameter                                                                      | 2 μm IGBT<br>(# 153) | 5 μm IGBT<br>(# 164) |

|--------------------------------------------------------------------------------|----------------------|----------------------|

| Forward drop at 20 A, 25°C $(V_{GE} = 20 \text{ V})$                           | 5.52 V               | 7.12 V               |

| Turn-off energy loss at<br>10 kV, 10 A and 25°C<br>(R <sub>G(ON)</sub> = 10 Ω) | 20.4 mJ              | 7.2 mJ               |

Fig. 2.18: Double pulse tester (14 kV peak) used for characterizing the IGBTs (High voltage capacitors, IGBT under test, gate driver, hot plate and HV load inductors are shown).

#### 2.5 Power converter design considerations

The fundamental advantage of the 15 kV IGBT is simplification of the converters' topology, minimizing the converter system footprint, while considerably improving the efficiency and reliability. However the high dv/dt resulting from the deep punch-through design and the resulting turn-on current spike requires careful design of the converter system, particularly for the thinner field-stop buffer layer IGBT.

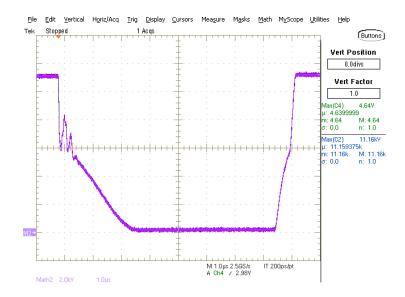

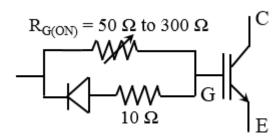

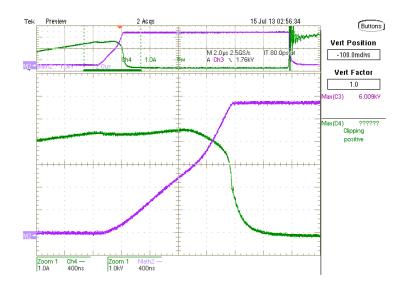

The high dv/dt (shown in Fig. 2.19) requires an ultralow coupling capacitance in the isolation power stage of the gate driver for common-mode noise immunity. The complete details of the gate driver design are provided in Chapter-3.

The turn-on di/dt (shown in Fig. 2.20) is in the order of 1 kA/µs, which can induce 1 V/nH (volt per nano Henry) in a nearby inductive loop in the control signal carriers or the printed circuit boards. The spurious tripping of the power converters system due to this di/dt noise needs to be minimized by using very low ESL decoupling capacitors. Similarly, the dv/dt of 100 kV/µs would generate 100 mA/pF (milli-ampere per pico-farad) ground current spikes due to the common mode capacitances of the converter system. The dv/dt induced common mode current should be minimized by reducing the coupling capacitances, or by constraining a path for these currents as discussed in the Chapter-4.

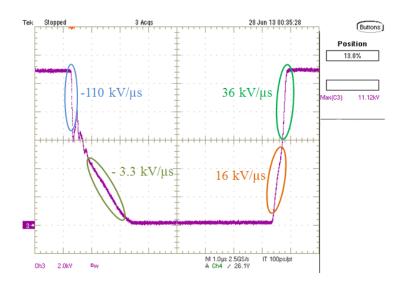

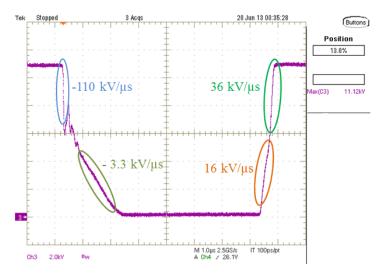

Fig. 2.19: Turn-on and turn-off switching voltage transitions with dv/dt values at 11 kV, for the 2 μm buffer layer thick 15 kV N-IGBT

Fig. 2.20: The current turn-on spike of 15 kV, 20 A, 2 μm buffer layer IGBT at 10 kV, 8 A and 25°C [Ch4 (Green): 10 A/div; time: 20 ns/div]

#### 2.6 Summary

A 14 kV double-pulse switching test setup has been built to characterize the 15 kV SiC N-IGBTs. The turn-on and turn-off switching tests are done up to 10 kV and 175°C with inductive, partly inductive and resistive load conditions. The 15 kV, 5 μm IGBT has negligible tail current with switching duration of about 800 ns at 10 kV, 10 A and 175°C. Based on the comparison of 5 μm buffer layer and 2 μm buffer layer IGBT, the 5 μm buffer layer IGBT is more suitable for high frequency power conversion due to lower turn-off loss and turn-on dv/dt, with almost equal dv/dt during turn-on and turn-off. The considerations for power converter design using these ultrahigh voltage devices, which exhibit two-slope voltage transitions during turn-on and turn-off, are provided. These results are basis for the gate driver development, IGBT heat-run tests and converter demonstrations presented in the next chapters.

### Chapter 3

# Gate Driver Design and Development for 15 kV SiC N-IGBT

#### 3.1 Introduction

As outlined in Chapter-2, the 15 kV SiC IGBTs, particularly the 2 µm field-stop buffer layer IGBT generates dv/dt over 100 kV/µs at the beginning of the turn-on switching transition. The high voltage and the high dv/dt present unprecedented challenges for designing the gate driver for these ultrahigh voltage IGBTs. The commercially available gate driver isolation power supplies have a maximum dielectric test voltage (50 Hz, 1 minute) of 18 kV rms [12]. These power supplies are meant for application to high voltage (4.5 kV or 6.5 kV) Si IGBTs based multilevel converters, where the dv/dt values and switching frequencies are expected to be considerably lower than that with the 15 kV SiC IGBTs. In [13], the high isolation gate driver design has been presented for 10 kV SiC MOSFETs. The ferrite-core isolation transformer is tested up to 26.8 kV dc while superposing 6.5 kV high frequency (non-square wave, low dv/dt) pulses. This gate driver is expected to withstand dv/dt of 50 kV/µs, which is generated by the 10 kV SiC MOSFETs. The gate driver was demonstrated on a solid state transformer (SSPS) [5], where the dv/dt values are lower than 50 kV/ $\mu$ s, due to soft-switched circuit. On the other hand, gate driver with 240 kV/µs dv/dt capability has been demonstrated at 400 V using PCB integrated capacitive coupling method [14]. However, the 15 kV SiC IGBTs present a different scenario with dv/dt greater than 100 kV/µs, and operating voltage up to 11 kV. Therefore, it is important to understand the available techniques to build a gate driver for these operating conditions including proper selection of logic ICs and voltage levels for good noise immunity. Also, the validation of the gate driver in high voltage, hard-switched, high frequency, high dv/dt test circuits is another critical element which is being addressed in this chapter.

#### 3.2 Gate Driver Development

#### 3.2.1 Design Criteria

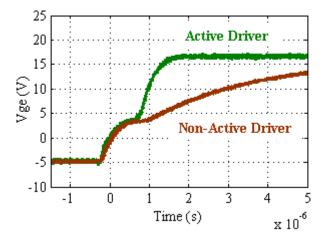

The clamped inductive turn-on and turn-off switching voltage transitions of the 15 kV, 20 A, 2  $\mu$ m field-stop buffer layer IGBT at 11 kV are shown in Fig. 3.1 (this figure is provided in chapter-2, but given again here due to its relevance to the topic). The turn-on device current is 5 A with gate resistance of 200  $\Omega$  (used to limit the dv/dt) and turn-off current is 10 A with gate resistance of 10  $\Omega$ . The turn-on dv/dt is high at the beginning of the transition, followed by a very slow fall in the voltage. The initial high dv/dt is due to extremely low depletion capacitance of the IGBT. About 6 kV, as the IGBT enters into diffusion mode (where the capacitance is significantly higher) the dv/dt is much lower. The high turn-on gate resistance,  $R_{G(ON)}$  used for limiting the initial dv/dt has significant influence in slowing down the dv/dt in the diffusion mode. The turn-off transition also has two different slopes with higher dv/dt over the punch through voltage. Limiting the turn-on dv/dt using a higher  $R_{G(ON)}$  would drastically increase energy loss. Therefore, the isolation stage of the high-side gate driver should be designed to handle this high dv/dt and high voltage.

Fig. 3.1: Turn-on and turn-off switching voltage transitions with dv/dt values at 11 kV, for the 2 μm buffer layer thick 15 kV N-IGBT (same as Fig. 2.19 shown in Chapter-2)

It has been determined to employ dc-dc isolation power supply for power isolation, and an optical transfer for signal isolation for designing the gate driver. This method has no duty cycle limitation to provide the bipolar gate voltages (typically +20V and -5V) and transformer saturation issues like in realizing the gate driver using the pulse transformers. There have been techniques proposed to address the transformer saturation [15]-[16], but they would increase the complexity of the gate driver design. Also, the need for high isolation with low coupling capacitance, to handle high dv/dt, increases leakage inductance which distorts the signal in the case of pulse transformers. However, using separate power isolation and signal isolation increases cost, which is of minor concern for these high voltage SiC IGBTs, which are suitable for over 100 kW applications, and the reliable operation of the gate driver is the foremost consideration. The design details of the isolation stage are discussed in the next subsections.

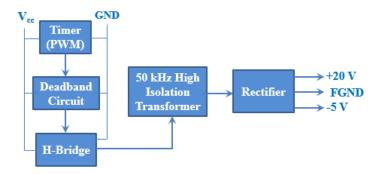

#### 3.2.2 High Isolation Power Supply Design

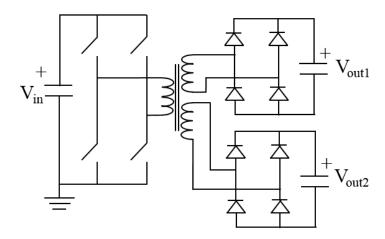

The high isolation dc-dc power supply is designed with the circuit schematic shown in Fig. 3.2. The primary side H-Bridge provides a 50 kHz square wave to the isolation transformer. The two secondary windings have individual diode rectifier stages to generate +20 V supply for turn-on and -5 V supply for turn-off. There is absolutely no galvanic connection between the primary and secondary windings of the isolation stage, as the diode rectifier stages do not need any control supply (unlike the H-Bridge on the primary side).

The isolation transformer for this application has been studied using several off-the-shelf core materials and sizes with toroid shape. The cores that have been used for the study are shown in Fig. 3.3 and their properties are listed in Table. 3.1. The powder cores (high flux and kool mu) have been chosen to build the initial version of the isolation transformer due to their high B<sub>max</sub>, which minimizes the core size as given by equation (3.1). However, the transformer was drawing relatively large magnetizing current, due to very low relative permeability as shown by equation (3.2), which was thermally loading the logic ICs used for generating the high frequency square wave. Therefore, the transformer was redesigned with a nano-crystalline core, which reduced the magnetizing current to a low value due to its very high permeability.

However, in the later iteration, ferrite core has been chosen due to its high permeability and lower cost, which is the most optimal material for this application.

Fig. 3.2: Circuit schematic of the isolation stage of the gate driver.

Fig. 3.3: The cores evaluated for the isolation stage design of the high voltage gate driver. High flux (top left), Kool Mu (top right), Nano crystalline (center), Ferrite (bottom both).

Table 3.1: Specification of the different cores evaluated for the high isolation transformer.

| Core             | $\mu_{ m r}$ | B <sub>max</sub> | Outer diameter /Inner<br>diameter | Height  |

|------------------|--------------|------------------|-----------------------------------|---------|

| High Flux        | 60           | 1.50 T           | 51.7mm/ 30.9mm                    | 14.4 mm |

| Kool Mu          | 60           | 1.05 T           | 51.7mm/ 30.9mm                    | 14.4 mm |

| Nanocrystalline  | 40,000       | 1.20 T           | 65.6mm/ 46.6mm                    | 22.8 mm |

| Ferrite (normal) | 10,000       | 0.43 T           | 49.1mm/ 33.8mm                    | 15.9 mm |

| Ferrite (small)  | 10,000       | 0.43 T           | 36 mm/ 23 mm                      | 10 mm   |

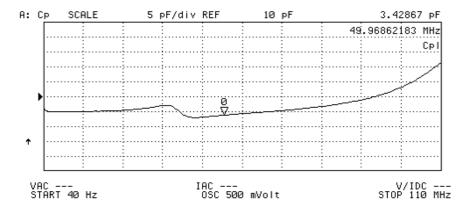

The size of the core is a very critical parameter in determining the inter-winding coupling capacitance. This was the reason why different sizes of ferrite have been investigated. But the larger size ferrite (bottom left in Fig. 3.3) was chosen to have higher safety margin from the perspective of isolation (corona discharge) between primary and secondary windings. Initially, high isolation has been achieved using high voltage wire, as shown in Fig. 3.4. However, the thicker insulation of the wire made it difficult to put large number of turns on the core, which is critical to reduce the magnetizing current. Therefore, the next version of transformer has been built by placing the insulation on the core with kapton polymide tape and using low voltage (thin) wire with increased number of windings. This helped in achieving flexibility in the transformer design, with reduced magnetizing current while achieving sufficient clearance between the windings. The low voltage wire is sufficient as the voltage per turn is low, and the high inter-winding voltage is possible due to high insulation provided by the kapton tape. The final version of the isolation transformer is designed by the ferrite core (shown in bottom left of Fig. 3.3). Fig. 3.5 shows the inter-winding coupling capacitance measured by an Agilent precision impedance analyzer. The capacitance is 3.4 pF and 13 pF at 50 MHz and 100 MHz respectively. Such low capacitance is critical to maintain signal integrity under the high dv/dt conditions.

$$B_{\text{max}}NA > LI_p$$

(3.1)

$$L = \mu N^2 A / l \tag{3.2}$$

Fig. 3.4: High isolation transformer designed using high voltage wire.

Fig. 3.5: The coupling capacitance curve with respect to frequency up to 110 MHz.

The dc-dc high isolation power supply is built using the transformer described above with two separate secondary windings, as shown in Fig. 3.2. The input voltage is chosen as 10 V dc to obtain better noise margin as explained in the next subsection. The output voltages are about +20 V and -5 V. This is obtained by connecting the negative terminal of the  $V_{out1}$  (20 V) to the positive terminal of  $V_{out2}$  (5 V).

#### 3.2.3 The Driver Stage Development

The selection of components that have high immunity to noise is very critical for operation of the gate driver circuit. As the MOS gate of the IGBT does not consume considerable amount of power (about a watt is sufficient), the off-the-shelf ICs, meant for low voltage, low power applications, have been sufficient to build the isolation power conversion stage for the gate driver. To maintain good signal fidelity,  $V_{cc}$  of 10 V has been chosen for most of the ICs. The high  $V_{cc}$  in combination with good noise margins of the CMOS logic levels (in contrast to lower noise margin TTL logic at 5 V) are pivotal in maintaining integrity of the signals. The de-coupling capacitors used in the circuit (for both isolation and driver stages) have extremely low ESL of < 400 pH, which are placed close to the  $V_{cc}$ /ground pins of the ICs.

The PWM input to the driver stage is transferred from the DSP controller using fiber optic cable and optical transmitter/receiver. This method of signal transfer is extremely reliable as there is no limit on either isolation voltage or dv/dt (when the receiver and transmitter are provided with power supplies having necessary isolation). However, as the  $V_{cc}$  of the optical receiver and transmitter of the off-the-shelf components is typically limited to 5 V, the driver stage (in contrast to the isolation stage) is provided with  $V_{cc}$  of 5 V. Therefore, PCB design was done with ground planes for low inductance to ensure reliability of the signals due to the lower noise margins presented by  $V_{cc}$  of 5 V.

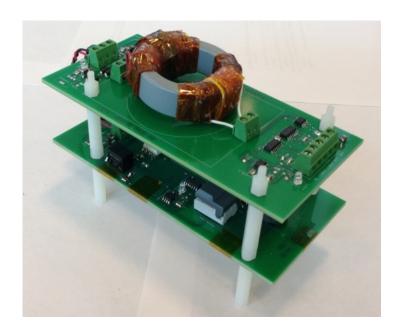

As mentioned earlier, the gate voltage ( $V_{GE}$ ) requirement for the SiC IGBT is  $\pm 20$  V and  $\pm 5$  V for turn-on and turn-off respectively. Unlike the case of Si device, the SiC devices require  $V_{GE}$  of about  $\pm 20$  V during turn-on to minimize the conduction loss [17]. Fig. 3.6 shows the prototype gate driver built with all these considerations. The top PCB in the picture is the dc to dc isolated power supply stage; whereas the bottom PCB is the driving stage with optical receiver for the PWM.

Fig. 3.6: The high voltage gate driver prototype for the 15 kV SiC IGBT.

#### 3.3 Experimental Validation

The fundamental challenge in validating the gate driver prototype is availability of high voltage (> 10 kV) high power dc source. Therefore, initial tests on the driver were performed on a clamped inductive double-pulse test setup intended for characterizing the switching performance of the IGBT. The tests were carried out by a high voltage and low current (10 mA) dc source storing the required amount of energy for two switching pulses in a string of high voltage film capacitors. The test circuit is a simple half-bridge converter with purely inductive load, with the 2 µm field-stop buffer layer IGBT on high-side so that the gate driver is exposed to high voltage and high dv/dt, as shown in Fig. 3.7. The switching voltage waveform of the IGBT at 11 kV on this test setup is shown in Fig. 3.8, which is identical to the waveform shown in Fig. 3.1. It should be noted that the gate voltage measurement is practically limited due to unavailability of a low voltage differential probe with very high isolation. The validation of the gate driver is confirmed from the operation of the circuit. Despite the confirmation from this test that the driver circuit can reliably transfer the gate

pulses with desired isolation and dv/dt capability, the robustness of the gate driver cannot be confirmed unless a continuous switching frequency test is performed.

Fig. 3.7: The half-bridge test circuit schematic used for 11 kV double-pulse validation of the gate driver.

Fig. 3.8: The high-side IGBT (2  $\mu$ m buffer layer) switching waveform at 11 kV validating the gate driver (waveform measured using single-ended probe and math function on the oscilloscope)

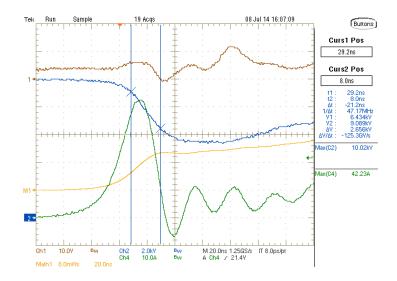

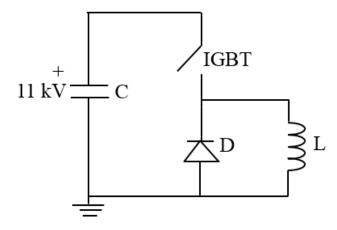

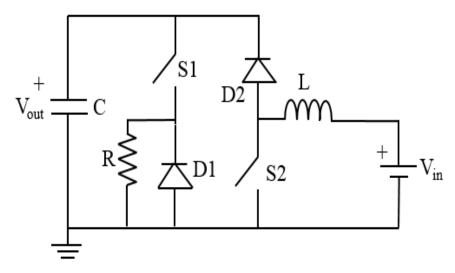

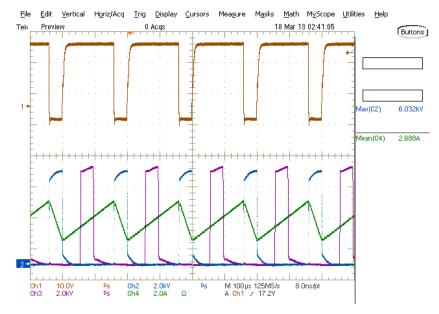

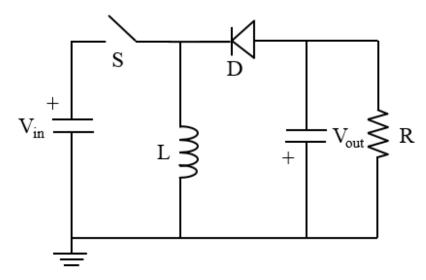

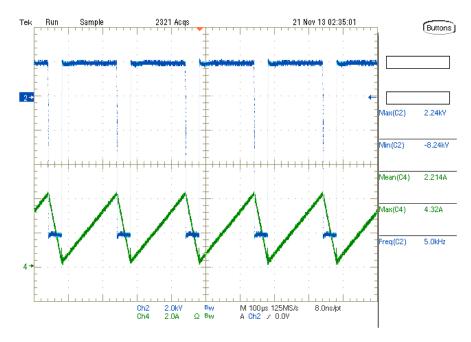

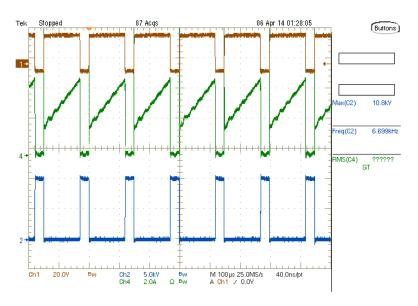

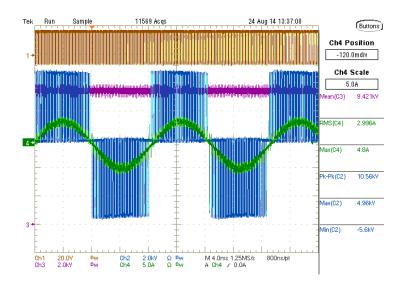

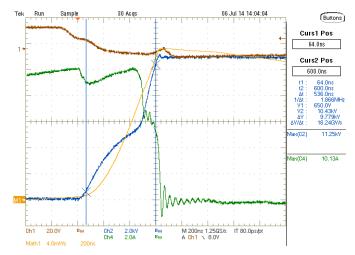

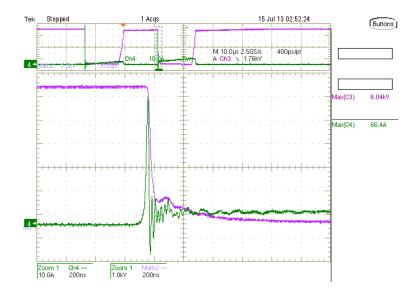

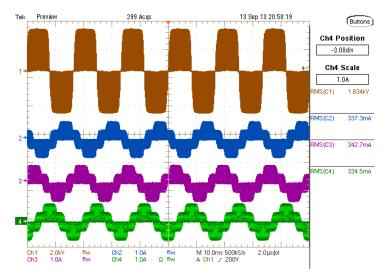

To perform continuous switching frequency tests on the gate driver, the high voltage, high current (not milli-ampere as in double pulse circuit) source is realized by a dc-dc boost converter with a 5 µm field-stop buffer layer IGBT. The input to the boost converter is a regulated laboratory high current, dc power supply of 3 kV, 50 A capability. A buck converter is realized on the same high voltage dc link, to avoid one more set of high voltage low ESL film capacitors, to test the gate driver, as shown in Fig. 3.9. The IGBT S2 and diode D2 form the boost topology for high voltage source realization; whereas, the IGBT S1 and diode D1 are used for buck topology for the gate driver tests. The inductance, L, has been designed with series connection of four individual high voltage inductors (each with a value of about 20 mH) to provide an effective inductance of about 80 mH. The duty cycle of the boost and buck converters are 80 % and 20 % respectively. The corresponding boost and buck converter waveforms at 6 kV dc link and at 5 kHz switching frequency on both boost and buck converters, validating the gate driver (on S1) are shown in Fig. 3.10.

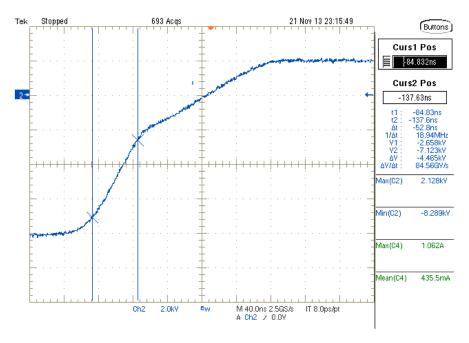

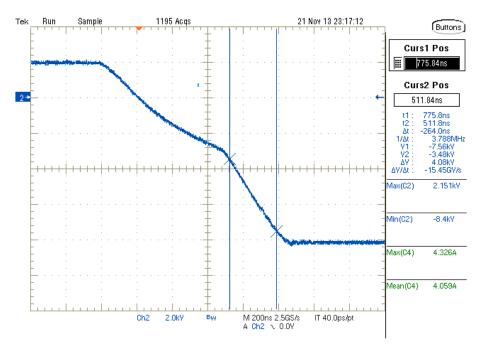

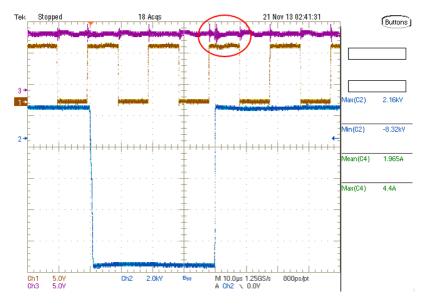

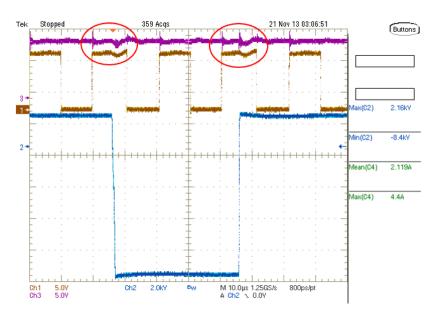

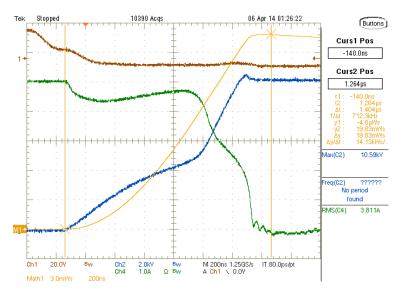

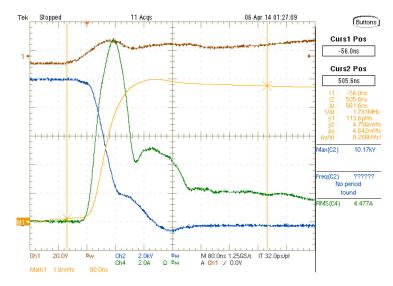

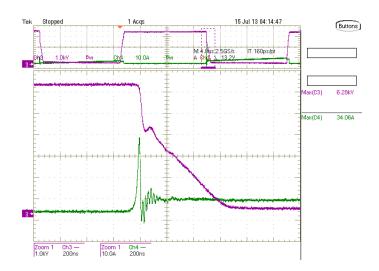

The boost converter fed buck converter has drawback of using two 15 kV SiC IGBTs and two HV diode modules. Also, an over voltage protection is needed on the high voltage dc bus to prevent damage of the boost converter switching devices in case of gate driver failure on the buck converter. In addition, it is critically important to save the SiC IGBTs, as they are research samples. Therefore, for higher voltage continuous frequency tests, buck-boost converter topology (shown in Fig. 3.11) has been used to evaluate the gate driver. This topology uses only one IGBT (5 µm field-stop buffer layer) and one diode. However, the IGBT will be stressed to the sum of input and output voltage; whereas, the gate driver sees maximum common mode voltage magnitude corresponding to the output voltage (for a step-up buckboost converter). The buck-boost converter is operated at 5 kHz with an input of 2 kV and output of 8 kV (80 % duty cycle). The IGBT is exposed to a continuous voltage stress of 10 kV at 5 kHz under these conditions. The gate driver is exposed to common-mode voltage of 2 kV when the IGBT is on; and -8 kV when the IGBT is off. The corresponding experimental waveforms of the inductor voltage (common-mode voltage seen by the gate driver) and current are shown in Fig. 3.12. This test has been carried out for a duration of 3 hours to validate reliable operation of the gate driver. The maximum turn-on and turn-off dv/dt are 85 kV/us

and 15 kV/ $\mu$ s respectively, as shown in Figs. 3.13 and 3.14, with  $R_{G(ON)}$  of 20  $\Omega$  and  $R_{G(OFF)}$  of 10  $\Omega$ . Table 3.2 summarizes all the above test conditions under which the gate driver is evaluated.

Fig. 3.9: The boost converter fed buck converter test circuit schematic used for 6 kV, 5 kHz validation of the gate driver.

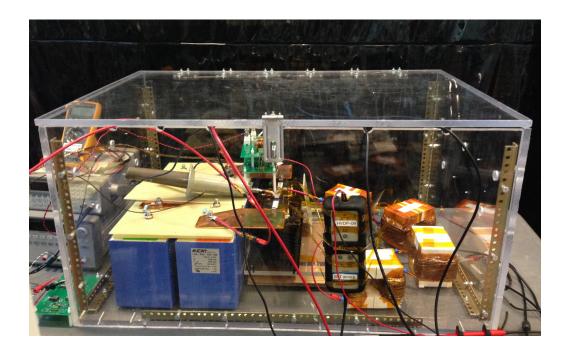

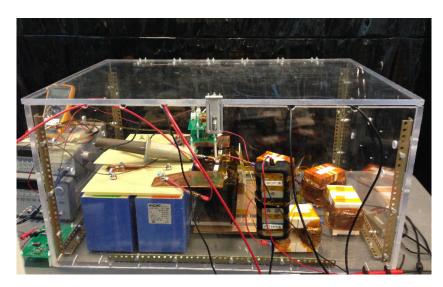

The test setup of the buck-boost converter is shown in Fig. 3.15, and of the double-pulse tests is shown in Chapter-2 (Fig. 2.18). The high voltage probes used are Tektronix 6015A 20 kV single-ended probes with 75 MHz bandwidth. The oscilloscope bandwidth is set to 150 MHz on the corresponding channels. It can be noticed from Fig. 3.10 that the HV single-ended probes are undercompensated during the boost converter fed buck converter tests. The probe compensation is adjusted for the buck-boost converter tests, and it is evident from the voltage waveform in Fig. 3.12.

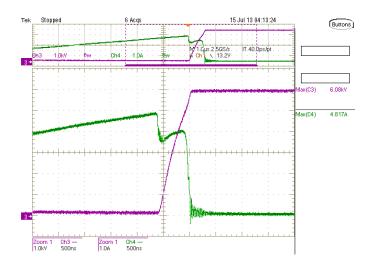

Fig. 3.10: Waveforms showing 6 kV, 5 kHz evaluation of the gate driver. (Ch1: V<sub>GE</sub> of 15 kV IGBT S2; Ch2: V<sub>CE</sub> of S2; Ch3: V<sub>CE</sub> of D1; Ch4: I<sub>L</sub>).

Fig. 3.11: The buck-boost converter schematic used for  $8\ kV$ ,  $5\ kHz$  validation of the gate driver.

Fig. 3.12: Waveforms showing 8 kV, 5 kHz evaluation of the gate driver. (Ch2: Isolation supply common mode voltage; Ch4: I<sub>L</sub>)

Fig. 3.13: Turn-on dv/dt during 8 kV, 5 kHz evaluation of the gate driver with  $R_{G(ON)} = 20 \Omega$ . (Ch2: Isolation supply common mode voltage)

Fig. 3.14: Turn-off dv/dt during 8 kV, 5 kHz evaluation of the gate driver with  $R_{G(OFF)} = 10$   $\Omega$ . (Ch2: Isolation supply common mode voltage)

Table 3.2: Summary of gate driver evaluation

| Test Procedure                           | Max<br>common-<br>mode<br>voltage | Max punch-<br>thru dv/dt | $R_{G(ON)}/R_{G(OFF)}$                                 | Duration<br>of Test |

|------------------------------------------|-----------------------------------|--------------------------|--------------------------------------------------------|---------------------|

| Double-Pulse                             | 11 kV                             | 110 kV/μs                | $\begin{array}{c} 200~\Omega/\\ 10~\Omega \end{array}$ | < 20 μs             |

| Boost converter<br>fed Buck<br>converter | 6 kV                              | <30 kV/μs                | 200 Ω/<br>10 Ω                                         | 5 minutes           |

| Buck-boost<br>converter                  | 8 kV                              | 85 kV/ μs                | 20 Ω/<br>10 Ω                                          | 3 hours             |

Fig. 3.15: Experimental setup of buck-boost converter used for 8 kV, 5 kHz validation of the gate driver.

#### 3.4 Robustness Evaluation of the Gate Driver