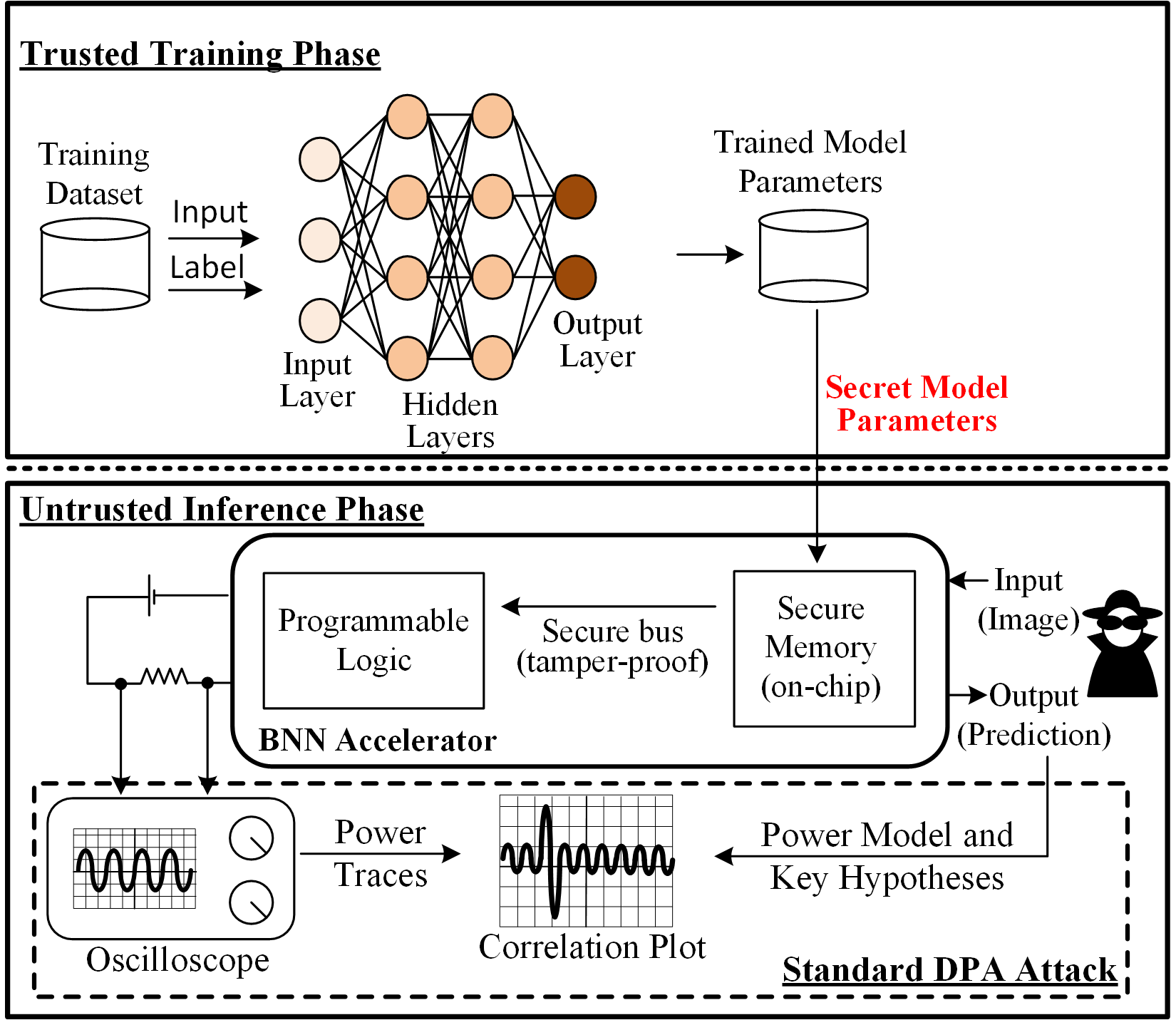

Differential Power Analysis of Deep Neural Networks with Mitigations at the Architecture Level

The objective of this project is to build architecture-level defenses through the use of compilers to automate side-channel resilient neural network implementations.

This project is funded by

SRC GRC Task 2908.

The liaisons for the project are Dr. Rosario Cammarota, Dr. Sohrab Aftabjahani, Dr. Vikram Suresh, Dr. Avinash Varna, Dr. Raghavan Kumar and Dr. Amitabh Das.

Our specific project link is private/requires sign in: https://www.src.org/library/research-catalog/2908.001/

Our work has been featured by the IEEE Spectrum Magazine.

PUBLICATIONS

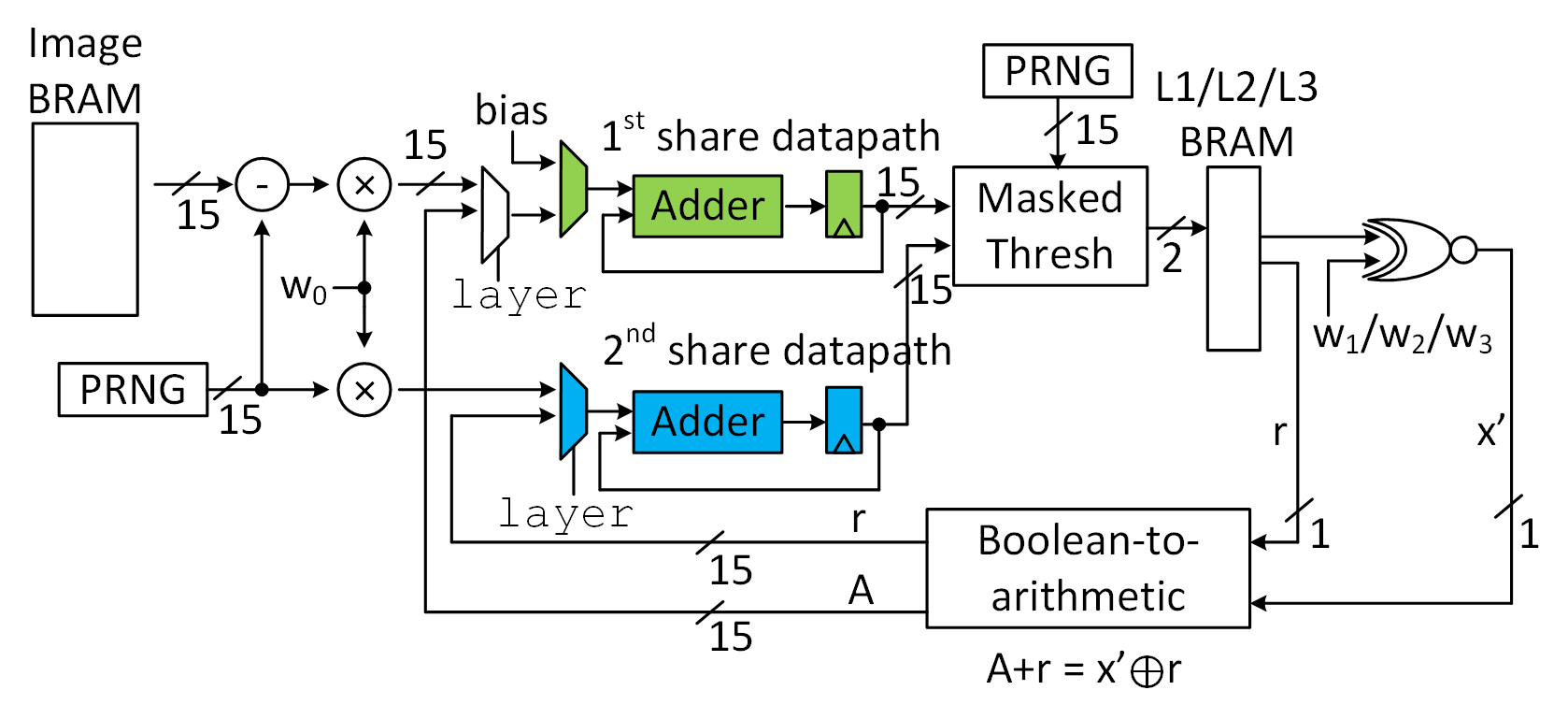

ModuloNET: Neural Networks Meet Modular Arithmetic for Efficient Hardware Masking

Anuj Dubey, Afzal Ahmad, Muhammad Adeel Pasha, Rosario Cammarota, Aydin Aysu

Journal Paper IACR Transactions on Cryptographic Hardware and Embedded Systems, Nov 2021.

Guarding Machine Learning Hardware Against Physical Side-Channel Attacks

Anuj Dubey, Rosario Cammarota, Vikram Suresh, Aydin Aysu

Journal Paper arXiv preprint arXiv:2109.00187, Sep 2021.

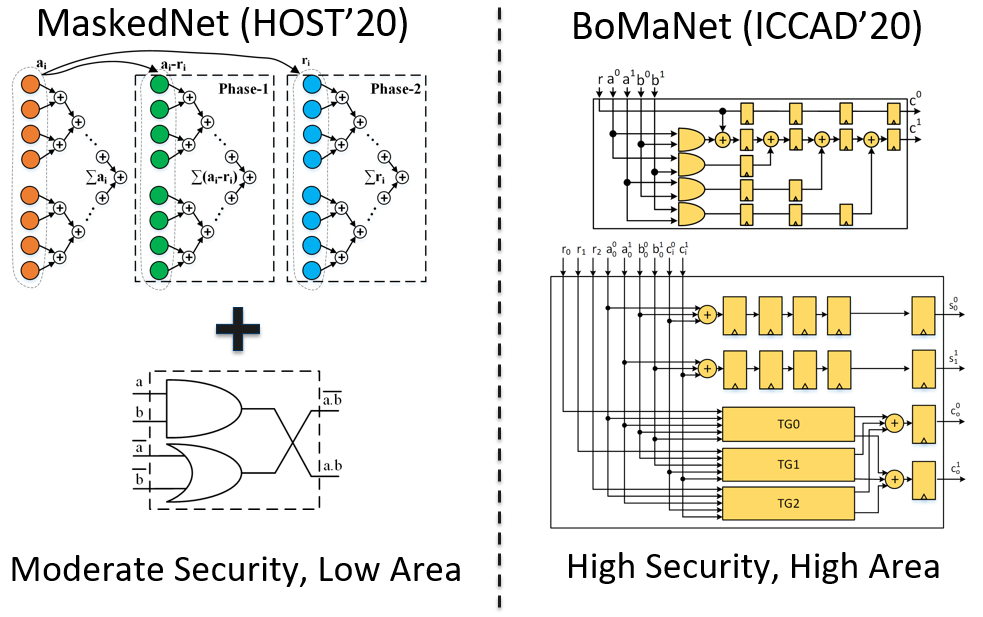

BoMaNet: Boolean Masking of an Entire Neural Network

Anuj Dubey, Rosario Cammarota, Aydin Aysu

Conference Paper International Conference on Computer-Aided Design (ICCAD), Virtual Conference, Nov 2020.

MaskedNet: A Pathway for Secure Inference against Power Side-Channel Attacks

Anuj Dubey, Rosario Cammarota, Aydin Aysu

Conference Paper IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Virtual Conference, Dec 2020.